Non ci sono prodotti a carrello.

di Matt Hein, Applications Manager, Brushless-DC Motor Drives, Texas Instruments

Una delle parti più frustranti della progettazione di sistemi ad alta potenza sono i risultati spesso elusivi degli effetti parassitari. Questo si applica in particolare ai sistemi di azionamento per motore ad alta potenza in cui le grandi dimensioni dei progetti delle schede, dei componenti e le elevate correnti di uscita possono avere come effetto il ringing in uscita, un dimensionamento eccessivo dei componenti o disturbi elettromagnetici irradiati (EMI). In questo articolo, verrà utilizzato PSpice® per TI per simulare la causa potenziale degli effetti di elementi parassiti nel progetto di un azionamento per motore e verranno proposti suggerimenti di progettazione per mitigarne gli effetti negativi.

Che cos’è un progetto per azionamento per motore ad alta potenza?

Essendo completamente immerso nel mondo dei sistemi di azionamenti per motori, spesso do per scontato le basi dell’architettura di un sistema di azionamento del motore a seconda della sfida specifica da affrontare. Esistono due ottime ragioni perché l’analisi degli elementi parassiti diventi un aspetto fondamentale per i sistemi ad alta potenza.

Per prima cosa, una potenza elevata comporta anche una corrente elevata: la commutazione 1 A in un motore non ha gli stessi effetti della commutazione di 100 A. Con una corrente elevata, tutte le induttanze e le capacità parassite insite sulla scheda a circuito stampato (PCB) saltano fuori e iniziano a causare problemi. Più si tiene bassa la corrente, meno sono importanti questi componenti parassiti. Per un sistema con una potenza di uscita elevata definita, tuttavia, la corrente di uscita target è fissa: il progetto si trovò quindi su una rotta di collisione con qualsiasi induttanza e capacità parassita.

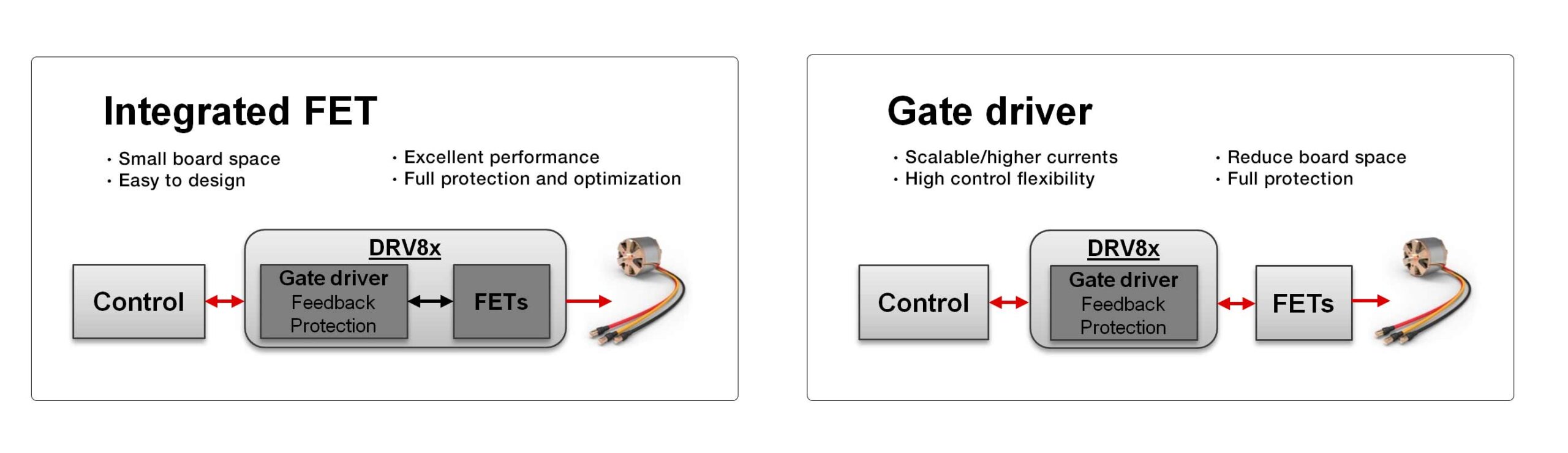

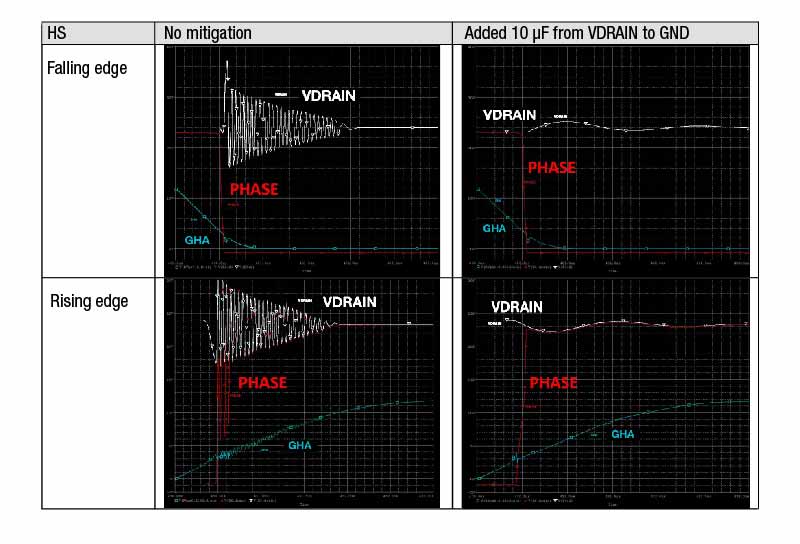

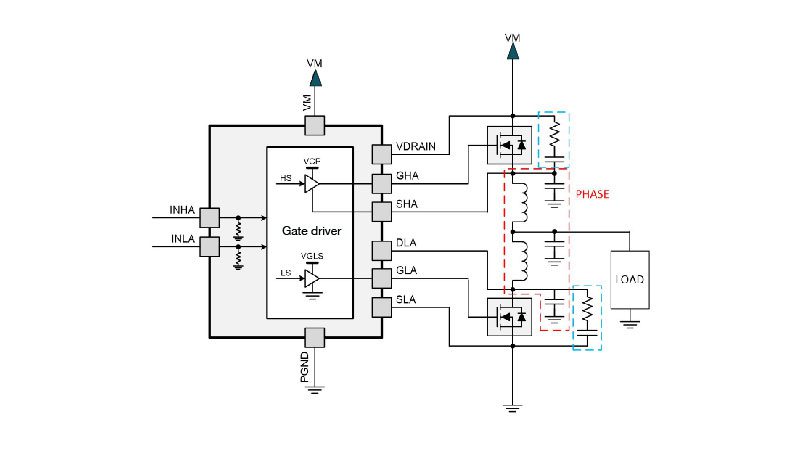

Secondariamente, i sistemi di azionamento per motore ad alta potenza richiedono un’architettura con driver del gate. Gli azionamenti per motori sono disponibili in due declinazioni: FET (transistor a effetto di campo) integrati e driver del gate con FET esterni – vedere la Figura 1. Gli azionamenti per motori con FET integrati sono molto efficaci per i sistemi a bassa potenza, in quanto integrano il driver del gate, lo stadio di potenza e ogni altro elemento di rilevamento e protezione in un singolo package. Questi dispositivi sono inoltre incredibilmente piccoli: ad esempio, il DRV8837C misura solo 2×2 mm, riducendo quindi sensibilmente gli elementi parassiti della scheda.

Purtroppo, non è possibile azionare un motore da 100 A neppure con le soluzioni a FET integrato a corrente più elevata (ad esempio, il DRV8873-Q1 è in grado di azionare fino a 10 A), pertanto è necessaria l’architettura con driver del gate. Utilizzando un driver del gate insieme a MOSFET esterni discreti per un sistema di azionamento per motore rimarrà sempre qualche traccia PCB fra i componenti sulla scheda che contribuirà agli effetti parassiti.

Figura 1. Confronto tra architetture a FET integrato e con driver del gate

Il circuito per driver del gate e l’impulso applicato

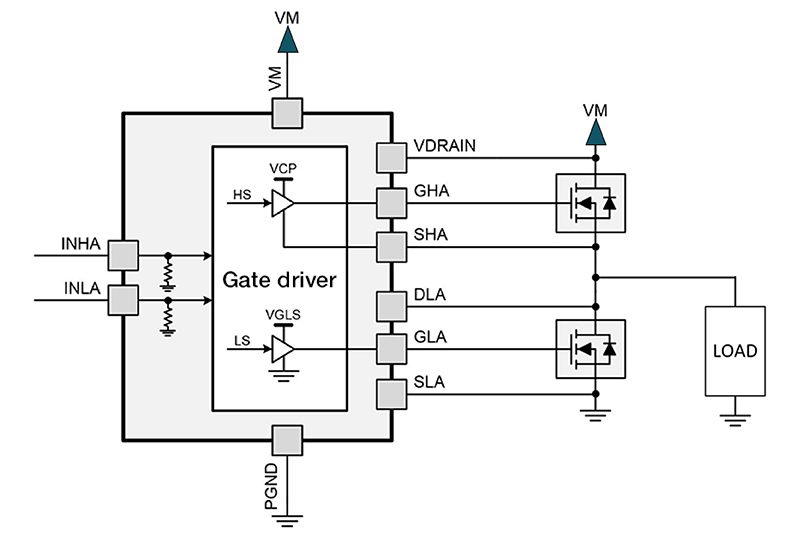

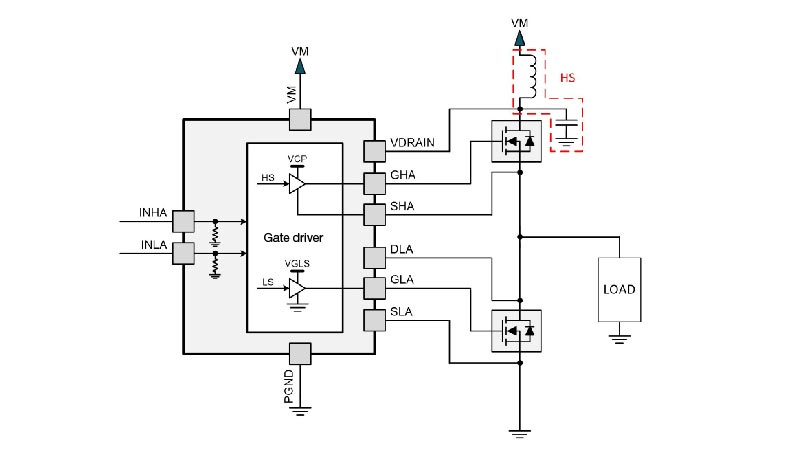

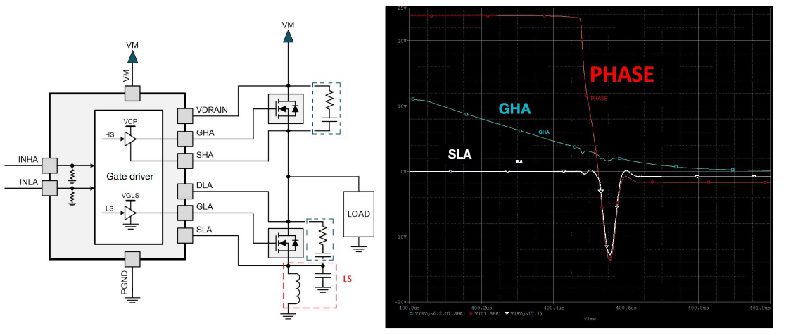

Per creare un circuito da analizzare, partiamo da un azionamento per motore half-bridge semplificato (Figura 2). L’azionamento del motore utilizzato in questo circuito è il DRV8343-Q1 di Texas Instruments (TI), un azionamento per motore di tipo smart gate trifase con amplificatori shunt di corrente. I MOSFET sono CSD18540Q5B di TI e la forza per l’azionamento del gate (IDRIVE) che ho scelto è 15 mA source e 30 mA sink. Ho utilizzato una sola fase e creato un carico modello (240 mΩ e 50 µH) per semplicità. L’alimentatore utilizzato in questo caso è a 24 V.

Figura 2. Circuito per driver semplificato (senza elementi parassiti)

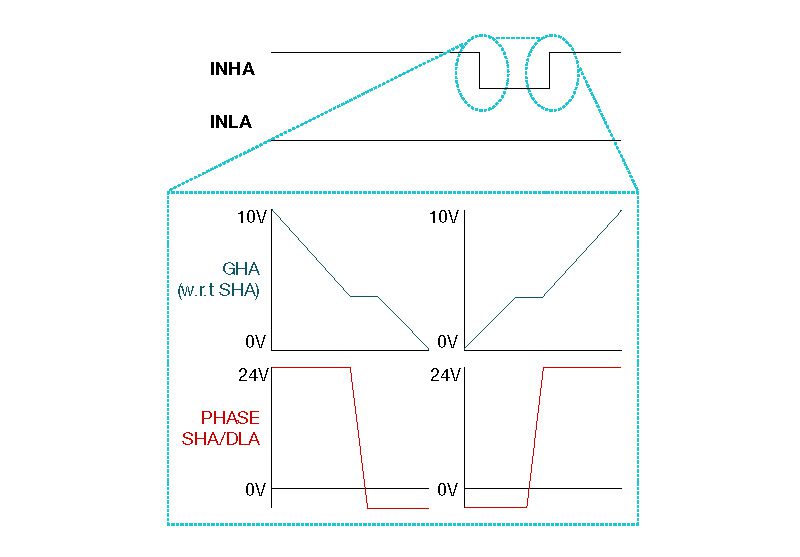

Quindi, ho simulato un «test di impulso», che comporta l’attivazione sul MOSFET high-side per un certo tempo, per poi attivarlo e disattivarlo rapidamente a impulsi mentre una corrente significativa attraversa il circuito. Simulando un test di impulso è possibile osservare eventuali effetti generati dai fronti di salita e di discesa dell’uscita quando il MOSFET high-side si disattiva e si riattiva.

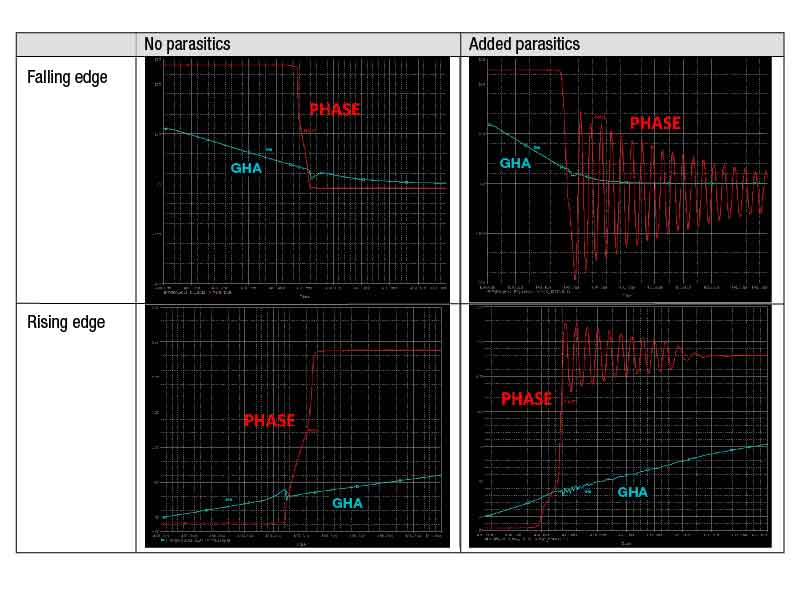

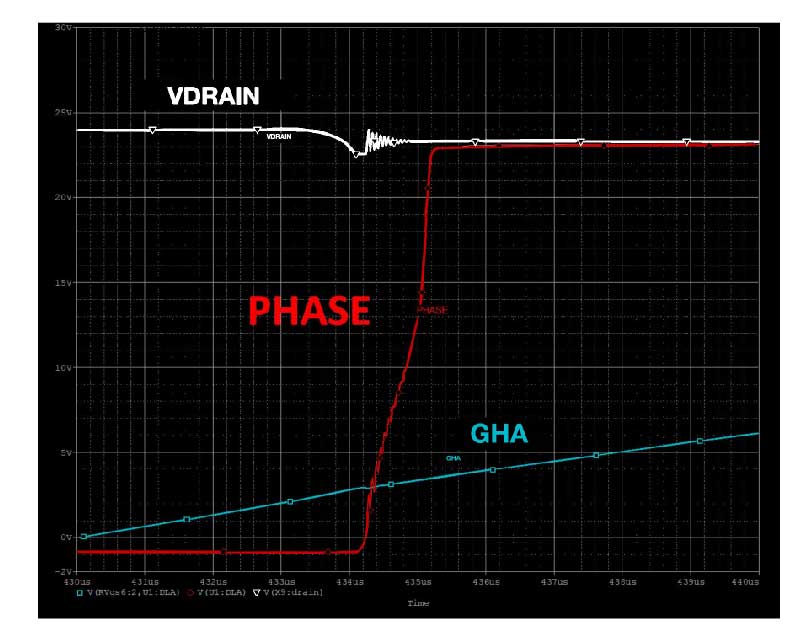

Nella Figura 3, è possibile vedere i segnali di controllo applicati, la forma d’onda ideale prevista per il gate high-side e la tensione di uscita. In questa simulazione, il MOSFET high-side è stato attivato per 400 µs, con impulso low per 30 µs e quindi riportato su high per i restanti 70 µs. Il MOSFET low-side è rimasto disattivato, pertanto l’eventuale corrente di passaggio è stata condotta attraverso il body diode del MOSFET low-side.

[boris]

Figura 3. Forma d’onda del test di impulso (senza elementi parassiti)

Aggiunta dei componenti parassiti e simulazione

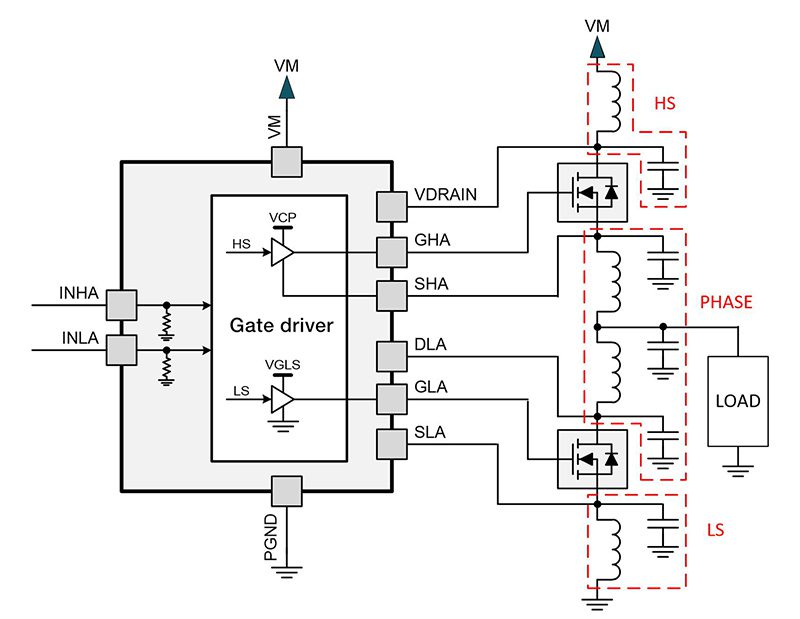

Se si aggiungono i componenti parassiti previsti in questo circuito, la complessità aumenta piuttosto rapidamente; lo schema circuitale non è più «bello» a vedersi. A tal fine, è necessario aggiungere importanti componenti parassiti in tre punti:

Fra l’alimentazione e il MOSFET high-side (HS).

Fra la massa e il MOSFET low-side (LS).

Fra il MOSFET high-side e low-side (PHASE).

È in queste tre posizioni che si vede tipicamente una grande traccia sul circuito stampato che corrisponde a una rete che porta una corrente elevata. Diamo un’occhiata alla Figura 4.

Figura 4. Circuito per driver con elementi parassiti

Ho utilizzato i seguenti valori degli elementi parassiti:

High-side (HS): 10 nF, 5 nH/10 mΩ.

Fase (PHASE): 2 nF, 2 nH/2 mΩ (per ciascun percorso, con 10 nF aggiuntivi sull’uscita per il carico).

Low-side (LS): 10 nF, 5 nH/10 mΩ.

Dal momento che questa è soltanto una simulazione, ho utilizzato delle induttanze e delle capacità parassite (potenzialmente) esagerate. È possibile progettare una scheda che limiti questi componenti parassiti, facilitando quindi la mitigazione (pur seguendo lo stesso processo). Al contrario, un circuito stampato con un progetto scarso potrebbe presentare un’induttanza e una capacità parassite sensibilmente maggiori che, a loro volta, possono rendere più difficile mitigare gli effetti parassiti. Per consultare le tecniche di layout per gli azionamenti per motore, consiglio la nota applicativa Best practice per il layout di schede per azionamenti per motore.

Quando ho simulato il circuito prima (Figura 2) e dopo (Figura 4) l’aggiunta di questi componenti parassiti, ho avuto la forte sensazione di aver danneggiato il circuito. Diamo un’occhiata alla Figura 5 per vedere una notevole oscillazione nella fase durante la commutazione su high o low. È importante mitigare questi effetti per proteggere il circuito dai danni (ad esempio da un picco di tensione negativa di –20 V) oppure per prevenire eventuali radiazioni elettromagnetiche indesiderate (le reti oscillanti fungono da antenne).

Figura 5. Risultati della simulazione PSpice per TI prima e dopo l’aggiunta di componenti parassiti

Per individuare i migliori interventi di mitigazione, andiamo ad analizzare i diversi componenti parassiti singolarmente e simulando gli effetti di ciascuno di essi.

Componenti parassiti fra l’alimentazione e il MOSFET high-side (HS)

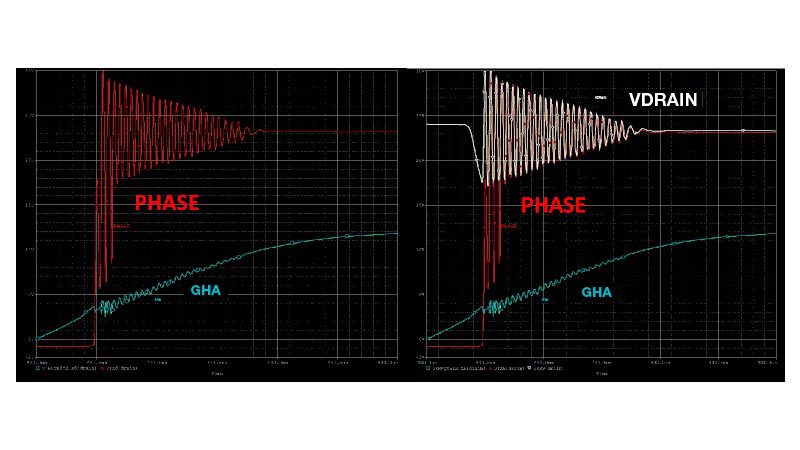

Quando ho aggiunto i componenti parassiti fra l’alimentazione e il MOSFET high-side (Figura 6), la simulazione ha mostrato un oscillazione molto evidente sull’uscita del fronte di salita (Figura 7). Andando più in dettaglio, è possibile vedere come l’oscillazione provenga dal drain del MOSFET high-side (VDRAIN). Nel fronte di discesa, dove il MOSFET high-side è spento, si vedrà lo stesso effetto, nonostante l’uscita non sia interessata.

Figura 6. Circuito di azionamento con elementi parassiti sul percorso high-side (HS)

Figura 7. Simulazione del fronte di salita con elementi parassiti aggiunti al percorso high-side (HS)

Questo stadio, si potrebbe pensare di dover aggiungere dei soppressori oppure che lo slew rate sia troppo alto e debba essere ridotto. Occorre considerare che i soppressori risultano più efficaci nel ridurre le oscillazioni di fase, e non le oscillazioni VDRAIN. Per esaminare la questione, ho implementato un soppressore da 1,2 Ω e 33 nF su entrambi i MOSFET high-side e low-side. È possibile vedere l’effetto nella Figura 8, dove il VDRAIN continua a scendere prima dell’evento di commutazione; pertanto, questo non è il metodo migliore per mitigare il ringing.

Figura 8. Nonostante i soppressore, la mitigazione non è efficace, per via delle oscillazioni su VDRAIN

Per saperne di più sulla progettazione con soppressore, è possibile leggere l’articolo tecnico Suggerimenti per la potenza: come calcolare un soppressore R-C in sette passaggi.

Un’altra soluzione possibile per ridurre l’oscillazione consiste nel ridurre lo slew rate, che nella simulazione va a ridurre sensibilmente il ringing, ma senza eliminarlo (Figura 9). Uno slew rate ridotto risulta in maggiori perdite di potenza (componenti più caldi), per via delle maggiori perdite di commutazione, e deve essere evitato, se possibile. In questo esempio, ho ridotto la corrente di azionamento del gate da 15 mA source a 1,5 mA source: un tempo di salita 10 volte più lungo.

Figura 9. Nonostante la riduzione della corrente di azionamento del gate e l’aumento del tempo di salita, la mitigazione non è efficace per via della maggiore dissipazione di potenza e dell’oscillazione continua

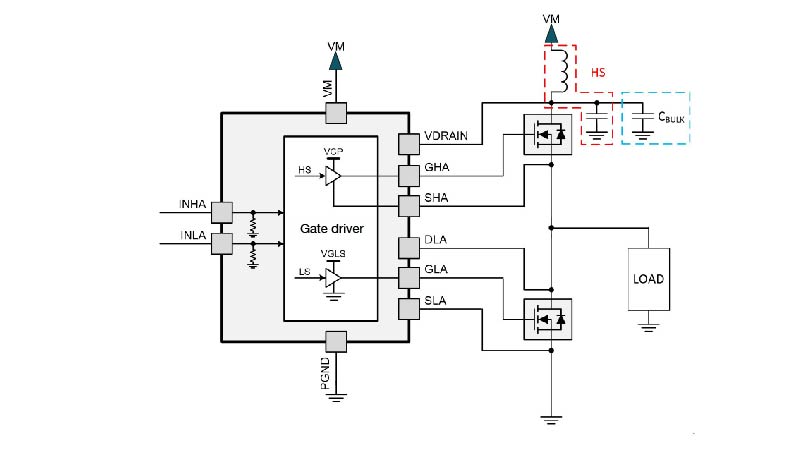

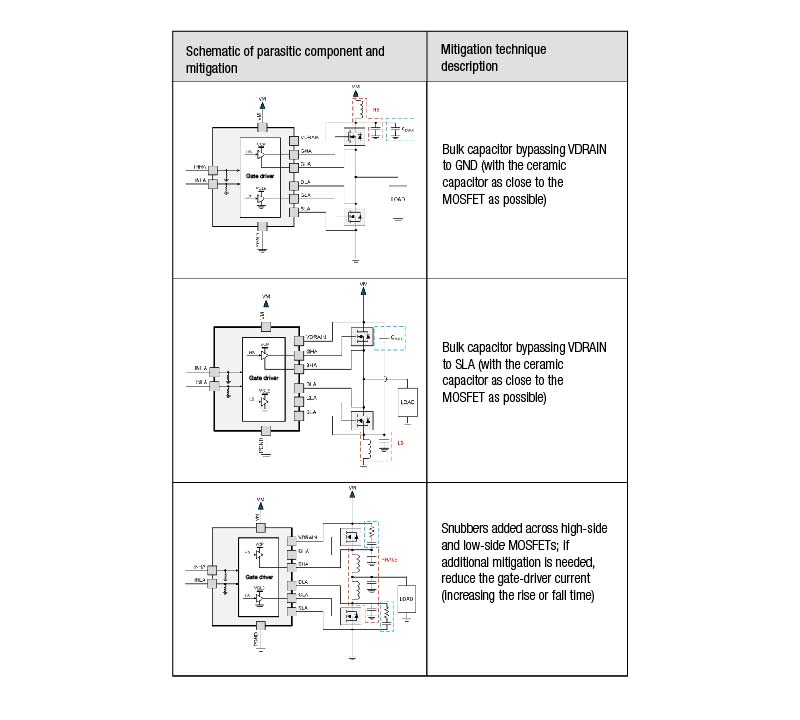

Per mitigare meglio questi effetti, aggiungiamo una grande capacità bulk sul nodo VDRAIN (Figura 10); in questo modo si rallenta sensibilmente l’oscillazione con una minore ampiezza. Semplicemente, ho reso molto, molto più lunga questa costante di tempo dell’induttore-condensatore. La Figura 11 mostra i risultati di questa aggiunta.

Nella simulazione, l’aggiunta del condensatore bulk ha fatto scendere l’oscillazione di picco da 37 V (13 V sopra l’alimentazione) ad un livello ben più gestibile di 25 V (1 V sopra l’alimentazione). Questo condensatore deve essere posto il più vicino possibile al MOSFET high-side per mitigare qualsiasi induttanza parassita supplementare fra il condensatore e il MOSFET. I condensatori ceramici sono preferibili per via della loro minore induttanza del conduttore e della migliore risposta ad alta frequenza.

Figura 10. Aggiunta di un condensatore bulk su VDRAIN

Figura 11. Mitigazione dei componenti parassiti high-side con un condensatore bulk (da VDRAIN a GND)

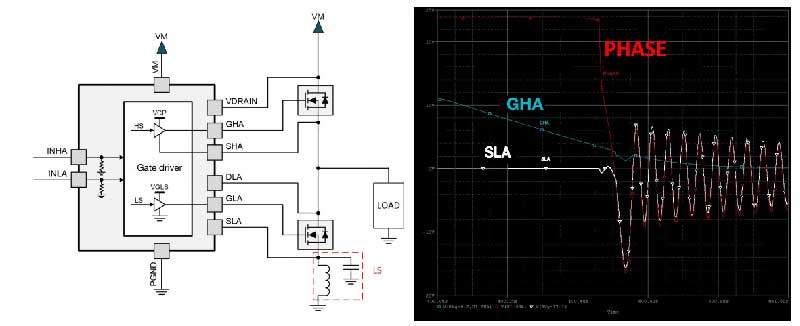

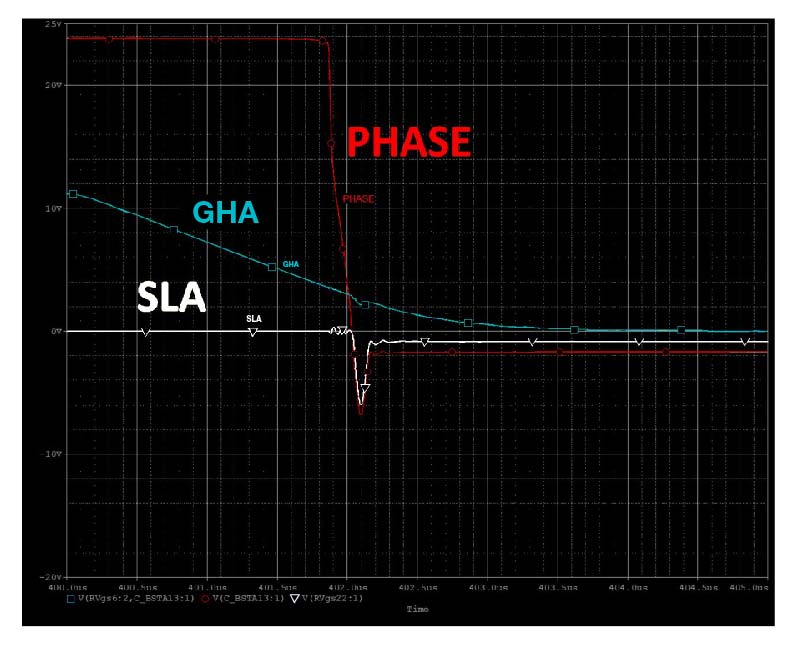

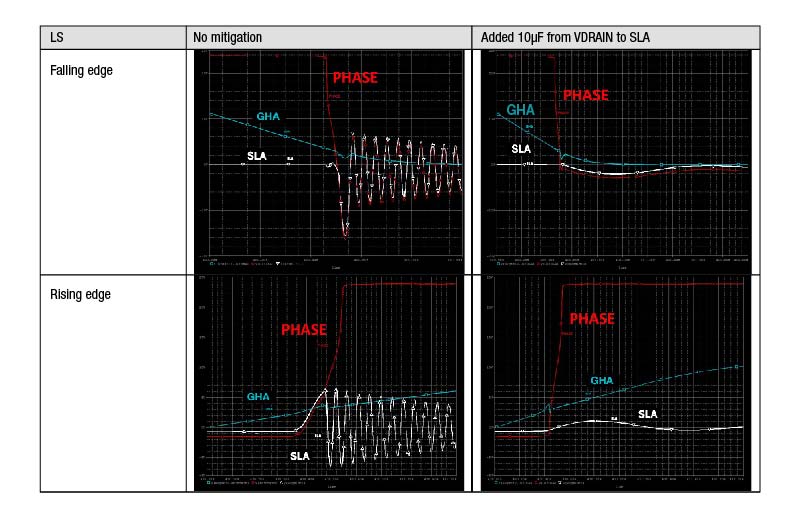

Componenti parassiti fra la massa e il MOSFET low-side (LS)

Il percorso low-side è quasi l’opposto rispetto al percorso high-side. I fronti di discesa hanno provocato oscillazioni significative, mentre i fronti di salita sono apparsi puliti. Ad un esame più attento, è possibile notare come il nodo di origine del MOSFET low-side (SLA) presentava del ringing sia sul fronte di salita che su quello di discesa (Figura 12).

Figura 12. Schema e simulazione con elementi parassiti aggiunti al percorso low-side (LS)

Di fronte a questa situazione, alcuni vorranno aggiungere soppressori o allungare il tempo di salita per contrastare il ringing, ma occorre evitare anche questo approccio in questo caso. Come ho fatto in precedenza, ho implementato un soppressore da 1,2 Ω e 33 nF su entrambi i MOSFET high-side e low-side. Il risultato è un drastico miglioramento delle oscillazioni sulla fase, ma rimane l’impulso iniziale di tensione negativa (Figura 13).

Figura 13. Nonostante i soppressori, l’attenuazione non è efficace a causa di un picco di tensione negativo

Se si riduce lo slew rate, il ringing si riduce sensibilmente (Figura 14). In questo esempio, la corrente di azionamento del gate è passata da un sink di 30 mA a un sink di 7 mA; ossia un tempo di salita >4 volte maggiore.

Figura 14. Nonostante la riduzione della corrente di azionamento del gate e l’aumento del tempo di salita, la mitigazione non è efficace per via della maggiore dissipazione di potenza

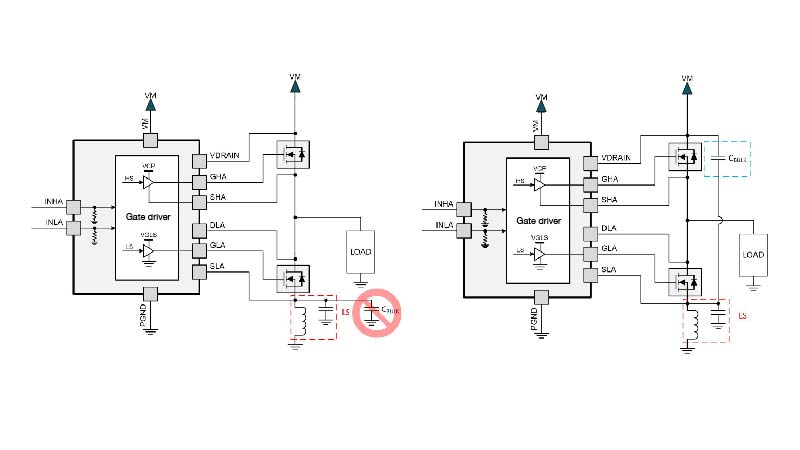

È possibile adottare un approccio simile al caso high-side e aggiungere ulteriore capacità bulk alla scheda per contrastare questo ringing. In questo caso, tuttavia, non è opportuno aggiungere un grande condensatore da SLA a massa. La maggior parte dei sistemi di azionamento per motore implementa il rilevamento della corrente sul low-side utilizzando un resistore di rilevamento della corrente e un amplificatore di rilevamento della corrente. Un tipico resistore di rilevamento nel package 2512 ha un’induttanza parassita da 1 a 5 nH, dando un certo credito ai valori parassiti da noi ipotizzati.

Un condensatore molto grande in parallelo con un resistore di rilevamento inibisce la capacità del sistema di rilevare correttamente la corrente (Figura 15). Il luogo giusto in cui aggiungere questo condensatore bulk è fra VDRAIN e sorgente low-side (SLA). Occorre tenere presente che, quando si aggiunge questo condensatore di disaccoppiamento, ci sarà ancora un certo effetto residuo sulla corrente di picco dovuto al resistore di rilevamento. Un valore molto elevato di questo condensatore avrà un impatto su qualsiasi limite di sovracorrente di picco che deriva dal rilevamento della corrente low-side.

Figura 15. Posizionamento errato (a sinistra) e corretto (a destra) di un condensatore bulk per mitigare gli elementi parassiti low-side

La Figura 16 mostra i risultati di questa aggiunta. Nella simulazione, l’aggiunta del condensatore bulk ha ridotto significativamente l’oscillazione del picco da –16 V a –3 V. Analogamente al caso precedente, questo condensatore deve essere posizionato il più vicino possibile al drain del MOSFET high-side e alla sorgente del MOSFET low-side per mitigare qualsiasi induttanza parassita supplementare tra il condensatore e i MOSFET. I condensatori ceramici sono preferibili anche in questo caso per via della loro minore induttanza del conduttore e della migliore risposta ad alta frequenza.

Figura 16. Mitigazione dei componenti parassiti low-side con un condensatore bulk (da VDRAIN a SLA)

Componenti parassiti fra i MOSFET (PHASE)

Probabilmente avete imparato che è opportuno tenere sempre i MOSFET high-side e low-side il più vicini possibile al fine di ridurre al minimo gli effetti parassiti durante la commutazione. Si tratta di un ottimo consiglio, ma non è mai possibile eliminare completamente questi effetti negativi.

Anche le più efficaci soluzioni MOSFET a più die (vedere CSD88599Q5DC per esempio) hanno comunque una certa induttanza parassita e una certa capacità parassita tra i MOSFET high-side e low-side. La capacità di uscita del MOSFET (COSS) e la capacità del cavo motore (a lunghezze di cavo maggiori) possono contribuire in modo significativo alla capacità vista sul nodo di fase al di fuori del circuito stampato.

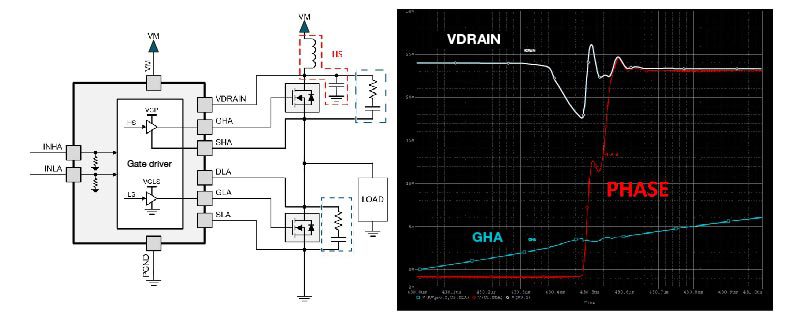

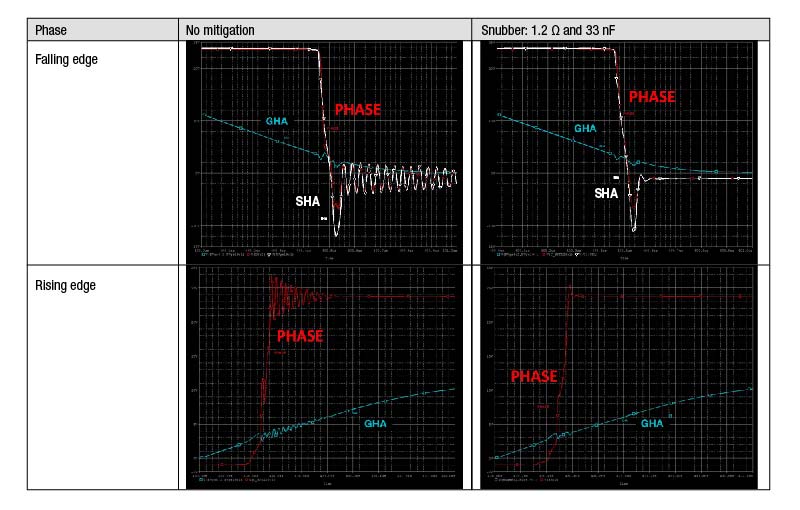

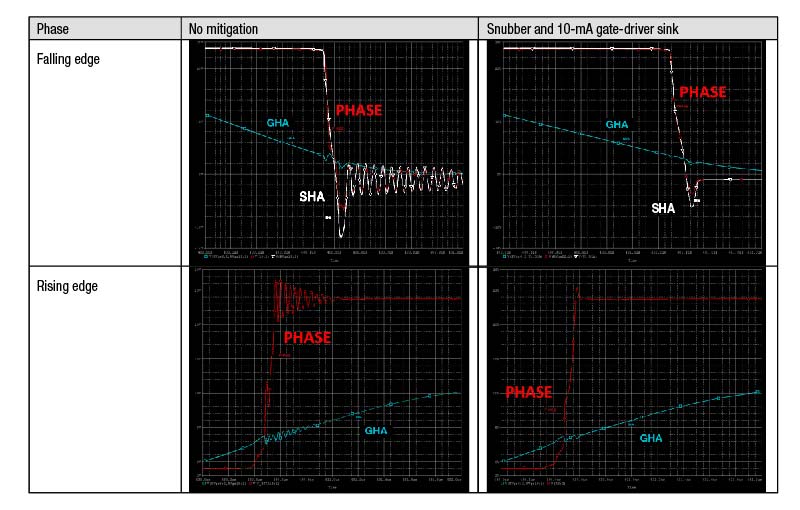

In questo caso, non è possibile aggiungere un’ulteriore capacità bulk al circuito per bypassare l’induttanza parassita. L’uscita verso il motore commuta su high e low e ulteriori grandi condensatori su questa rete si caricano e scaricano ripetutamente, creando una soluzione di sistema molto inefficiente. Quando questo accade, è meglio passare ai soppressori come prima strategia (Figura 17).

I sostenitori dei soppressori possono quindi tirare un sospiro di sollievo: è ora di usarli! Gli effetti dell’aggiunta di soppressori al circuito sono visibili nella Figura 18.

Figura 17. Schema elementi parassiti aggiunti al percorso di fase (PHASE) e soppressori aggiuntivi

Figura 18. Mitigazione dei componenti parassiti di fase con soppressori

Il soppressore risolve quasi completamente l’oscillazione sul fronte di salita e migliora notevolmente la situazione sul fronte di discesa. Come negli esperimenti precedenti, ho implementato un soppressore da 1,2 Ω e 33 nF su entrambi i MOSFET high-side e low-side. Tuttavia, proprio come nel caso degli elementi parassiti sul MOSFET low-side (Figura 14), rimane il primo impulso negativo.

A questo stadio, è possibile concludere che il tempo di discesa debba essere aumentato per superare completamente questi effetti parassiti. È necessario migliorare il picco di tensione negativa di –11 V sul fronte di discesa nella Figura 18 in modo da rimanere entro i valori massimi assoluti del DRV8343-Q1 (–7 V per 200 ns). Quando si riduce il sink di corrente dell’azionamento del gate da 30 mA a 10 mA si ottiene questo picco negativo entro il valore massimo (Figura 19).

Figura 19. Mitigazione dei componenti parassiti di fase con soppressori e un ridotto sink di corrente di azionamento del gate

Riepilogo

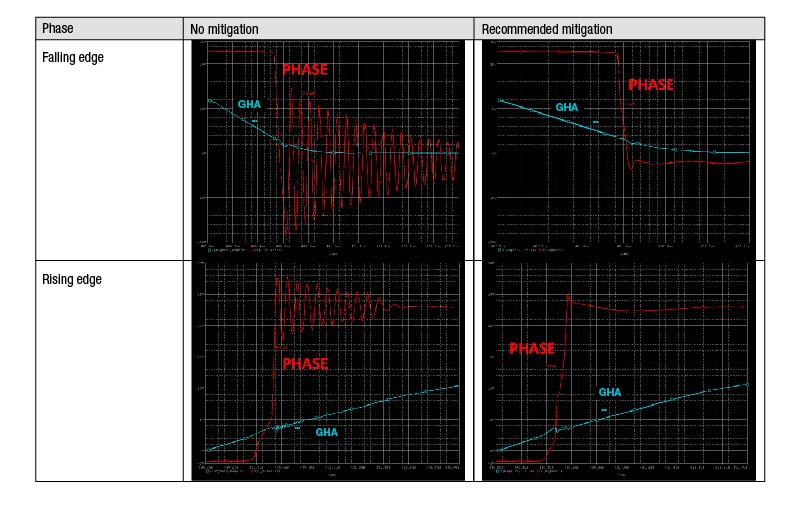

In definitiva, che cosa abbiamo imparato da questo esercizio di simulazione? Per questi tre effetti parassiti comuni (high-side, low-side e fase) esistono tre diverse tecniche di mitigazione. Se si applicano tutte le tecniche di mitigazione descritte in questo articolo al circuito con tutti i componenti parassiti inclusi (Tabella 1), è possibile ridurre significativamente l’overshoot, l’undershoot e il ringing (Figura 20).

Tabella 1. Riepilogo delle tecniche di mitigazione dei componenti parassiti

Figura 20. Mitigazione di tutti i componenti parassiti utilizzando i metodi descritti

Questo è stato per me un esercizio particolarmente divertente, in quanto mi ha dato una grande opportunità per provare gli schemi e le capacità di simulazione dello Strumento di simulazione PSpice per TI. Queste simulazioni sono molto più facili e veloci da eseguire rispetto agli esperimenti fisici su scheda e possono fornire molte informazioni su cosa fare quando si incontrano problemi nel mondo reale con gli elementi parassiti della scheda.

[/boris]