Di Ahmed Noeman [System Engineer, Factory Automation and Control]

La modulazione di larghezza di impulso (PWM) è un diffuso metodo di progettazione per rappresentare la tensione nell’elettronica di controllo, in quanto controllare l’accuratezza di temporizzazione nei circuiti integrati risulta più semplice che controllare l’accuratezza della tensione. I separatori di clock digitali integrati possono generare frazioni accurate partendo da riferimenti di clock molto più facilmente di quanto possa fare un tipico convertitore analogico/digitale (ADC) partendo da un riferimento di tensione. Il controllo PWM è ampiamente utilizzato nella conversione di potenza, nel controllo della luminanza LED, nel controllo di motori e nelle telecomunicazioni.

I convertitori digitale/analogico (DAC) basati sulla PWM sono di uso comune nei trasmettitori di campo per la loro semplicità, robustezza e costo. Tuttavia, ottenere un’alta risoluzione su una larghezza di banda relativamente ampia è particolarmente impegnativo per la classica implementazione della PWM con DAC, in quanto un DAC richiede un clock a frequenza eccessivamente alta.

Questo articolo espone diverse tecniche per superare i classici limiti della PWM con DAC e come ridurre il consumo energetico; a seguire, sono descritte la progettazione e la convalida di uno stadio trasmettitore PWM ad alte prestazioni da 4 a 20 mA che utilizza queste tecniche.

Analisi di un segnale PWM

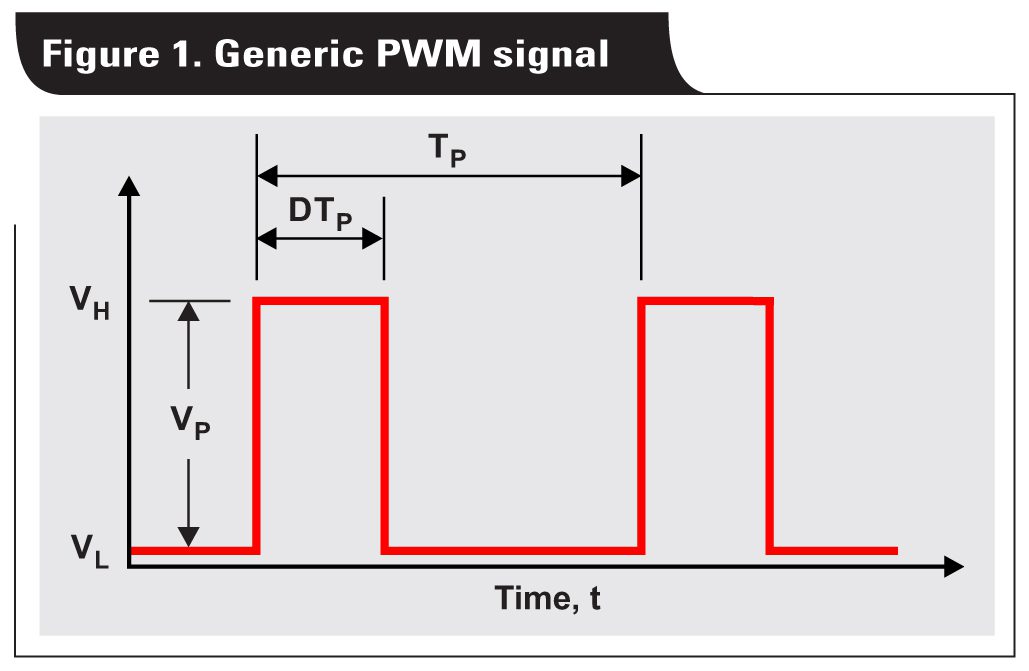

La Figura 1 mostra un segnale PWM generico con periodo (TP), ampiezza picco-picco (VP) e larghezza di impulso (DTP), dove D è una frazione compresa tra 0 e 1.

Le Equazioni 1 e 2 definiscono rispettivamente la frequenza PWM (fP) e VP.

dove VHe VLsono rispettivamente le tensioni alta e bassa dello stadio di uscita digitale.

Figura 1. Segnale PWM generico

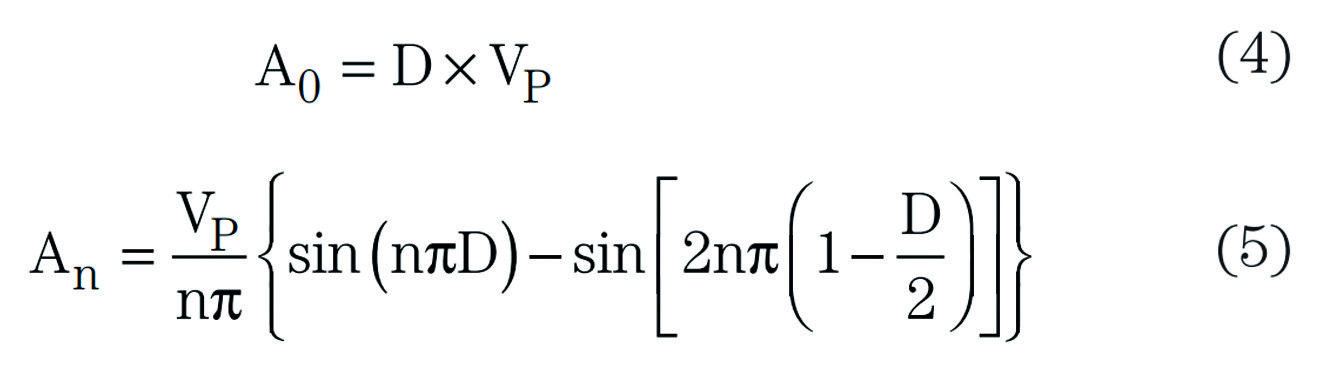

Allo stato stazionario, e con poca manipolazione matematica, l’Equazione 3 calcola la rappresentazione in serie di Fourier del precedente segnale PWM.

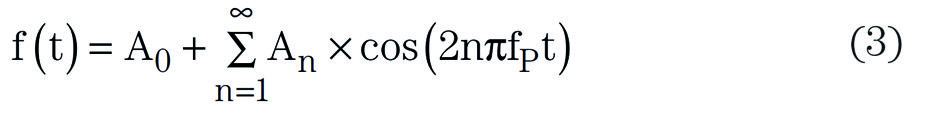

L’Equazione 3 contiene termini in CC e termini di armoniche di fP. Vedere il Riferimento 1 per il report applicativo che mostra ulteriori dettagli sulla derivazione. Di particolare interesse sono le grandezze di questi termini in CC e per le armoniche di frequenza PWM mostrate nella Figura 2.

Figura 2. Rappresentazione nel dominio di frequenza dei coefficienti della serie di Fourier per PWM

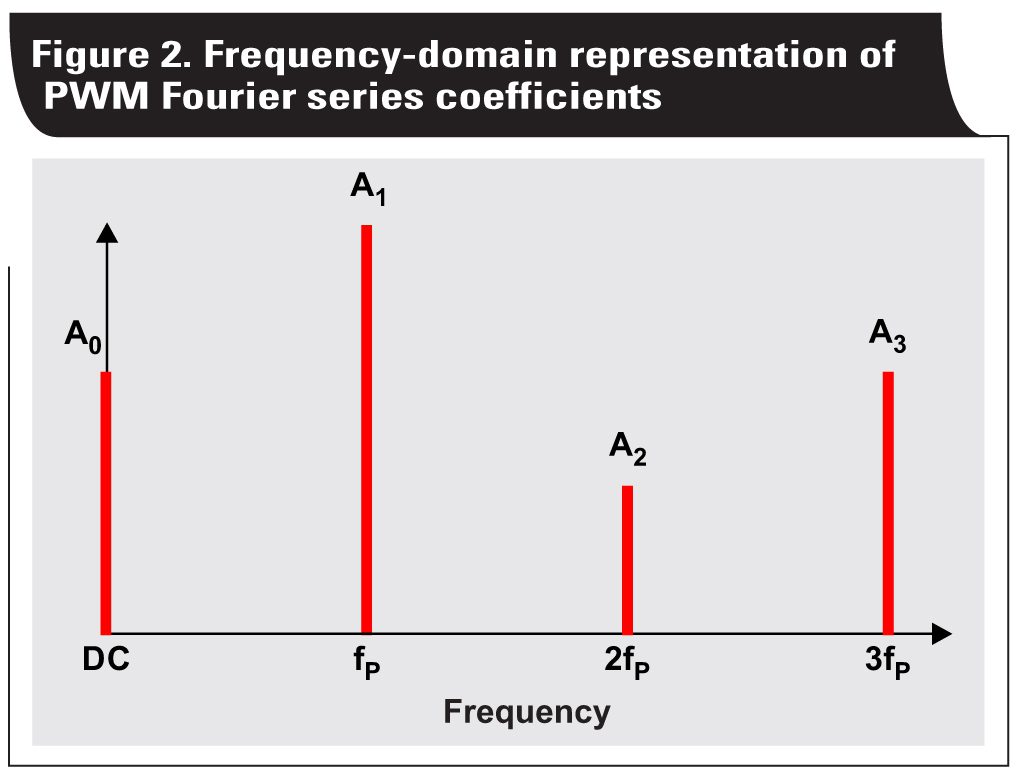

Le Equazioni 4 e 5 mostrano la CC e la grandezza dei termini armonici nel segnale PWM.

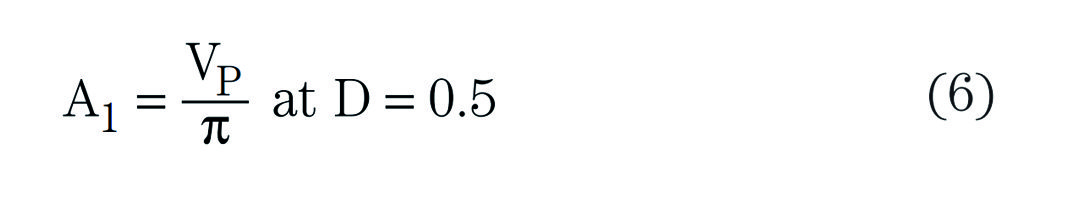

Il valore in CC A0è uguale alla grandezza picco-picco del segnale PWM moltiplicata per il duty cycle (D) e rappresenta l’output DAC desiderato. Gli altri termini di ordine superiore producono errori al di sopra dell’output desiderato; i loro valori dipendono sia da D che dall’ordine armonico (n). L’errore nel caso peggiore si verifica a causa di un’armonica di primo ordine quando D = 0,5, come mostrato nell’Equazione 6.

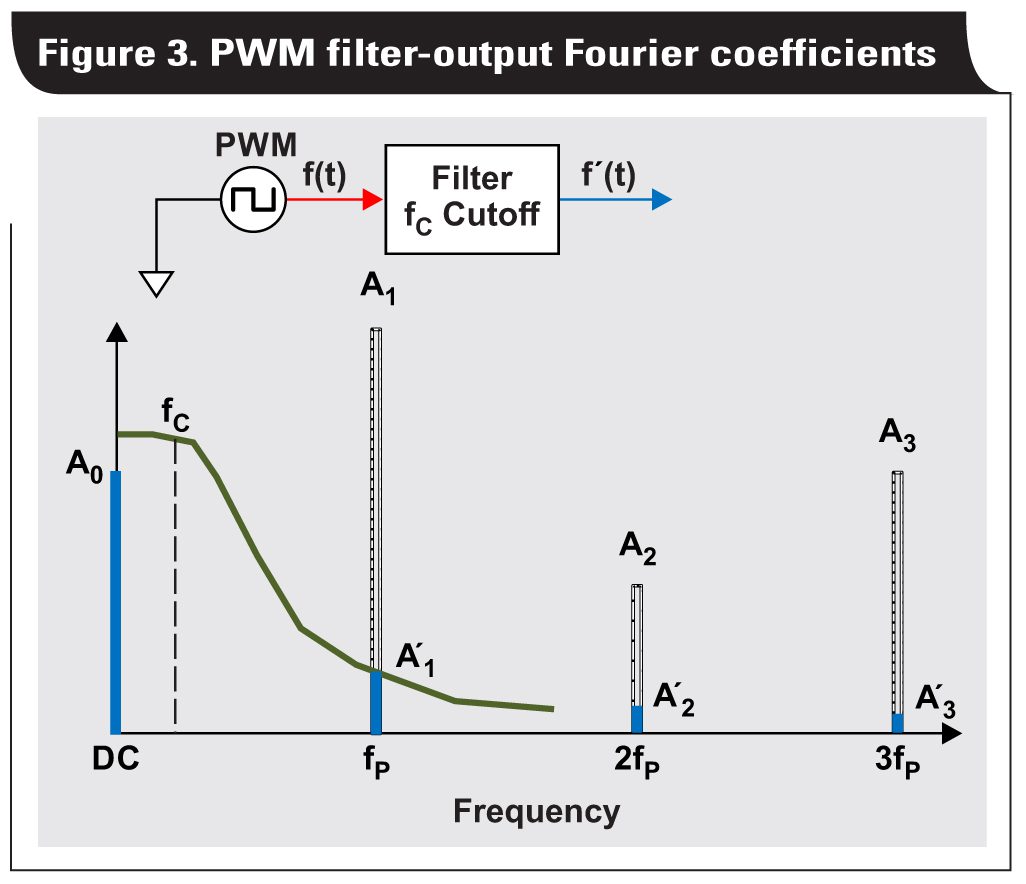

Le armoniche di ordine superiore sono tipicamente soppresse da un filtro passa-basso di ordine (m) e frequenza di taglio (fC). La Figura 3 mostra l’output di questo filtro passa-basso, rappresentato nell’Equazione 7.

Figura 3. Coefficienti di Fourier per output del filtro PWM

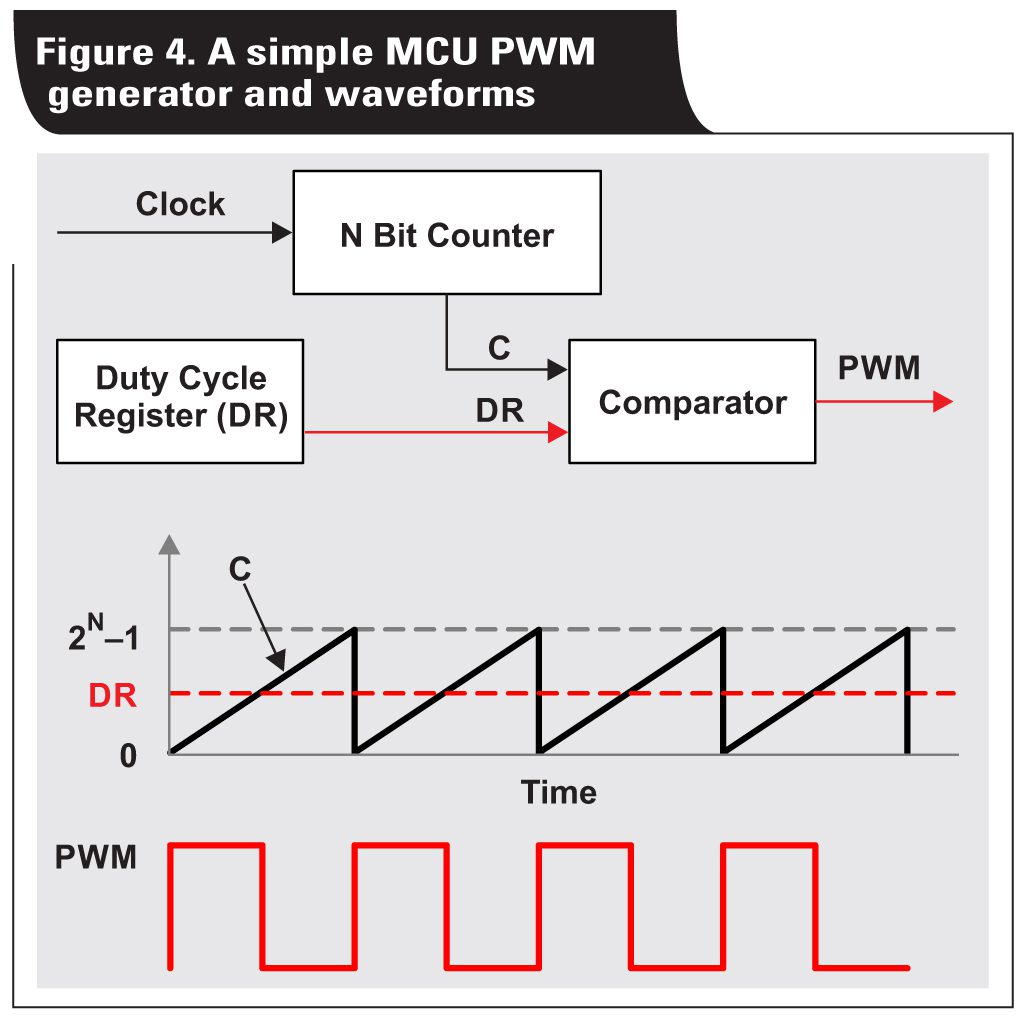

La maggior parte dei microcontroller (MCU) genera segnali PWM utilizzando una struttura hardware simile a quella mostrata nella Figura 4. In poche parole, un contatore, che conta a salire e si azzera quando viene raggiunto un limite specificato, determina il periodo e la frequenza PWM. Un altro livello impostato dal registro a duty-cycle determina quando l’uscita PWM passa da high a low. L’estratto del capitolo «Timer_A»[2] della MSP430™ User’s Guide[3] descrive questa struttura hardware, mentre la nota applicativa «Dual-Output 8-Bit PWM DAC Using Low-Memory MSP430 MCUs»[4] spiega come utilizzare l’hardware per generare segnali PWM. Con un generatore di segnali PWM di questo tipo, l’Equazione 8 rappresenta fP come:

dove fCLKè la frequenza di clock dell’MCU ed N è la profondità del contatore in bit.

Figura 4. Un semplice generatore PWM a MCU e forme d’onda

La struttura in Figura 4 implica l’esistenza di un valore minimo del duty cycle che può essere generato come espressione dell’Equazione 9.

L’Equazione 9 imposta l’incremento minimo (o la risoluzione minima) per un output DAC possibile utilizzando tale struttura. Tuttavia, l’incertezza dell’output supera la risoluzione per via delle componenti armoniche residue dopo il filtraggio. Le ondulazioni di uscita del filtro appaiono come rumore e riducono il numero effettivo di bit (ENOB) del DAC.

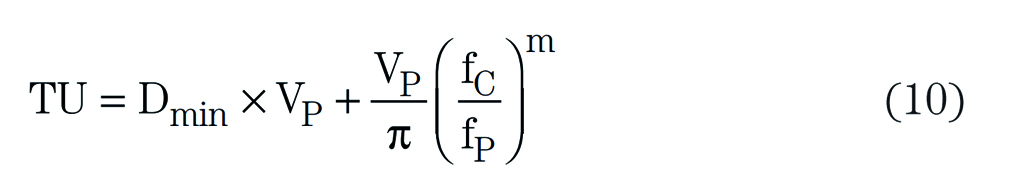

L’Equazione 10 definisce questa incertezza totale (TU, total uncertainty) come la somma della risoluzione minima e delle ondulazioni.

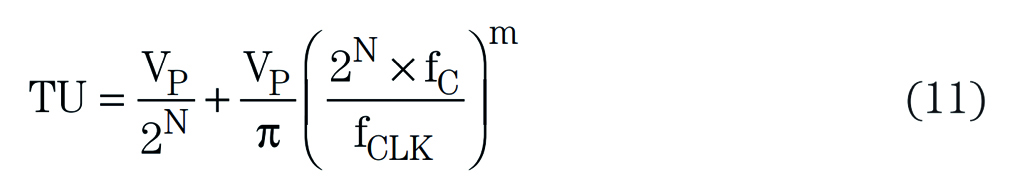

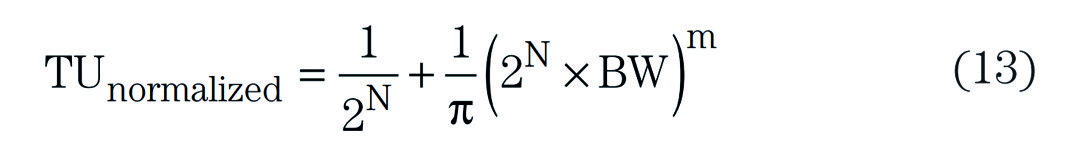

Sostituendo Dmin dell’Equazione 9 nell’Equazione 10 si ottiene l’Equazione 11.

L’Equazione 12 definisce la larghezza di banda relativa del filtro (BW).

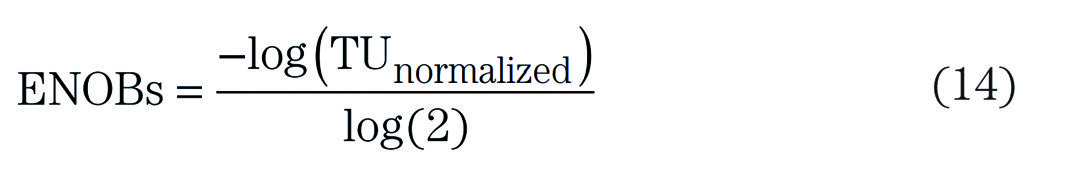

L’Equazione 13 riscrive l’incertezza in funzione di questa larghezza di banda relativa del filtro e la normalizza dividendola per il livello picco-picco.

L’Equazione 13 consente di scrivere gli ENOB in funzione della larghezza di banda relativa con l’Equazione 14.

Tracciando questa funzione con valori diversi per N ed m, come mostrato nella Figura 5, si mette in mostra un fatto interessante: l’architettura PWM presenta una limitazione intrinseca, andando a raggiungere un’elevata risoluzione su una larghezza di banda ragionevole. Ad esempio, se N = 12 bit e ipotizzando che fCLK = 16 MHz, è possibile ottenere solo ENOB a 12 bit (con fPWM = 4 kHz) utilizzando un filtro di terzo ordine, fino ad una larghezza di banda di 10–5 × 16 MHz = 160 Hz. Si tratta di un limite teorico che non tiene conto degli errori dovuti all’implementazione circuitale del filtro.

La tecnica PWM a due vie

[boris]

Per superare la limitazione intrinseca e abilitare la conversione ad alta risoluzione basata su PWM, altri hanno proposto il dithering e la modulazione stocastica PWM,[5] ma nessuno dei due ha un’implementazione pronta su una MCU standard. Un altro metodo prevede l’utilizzo di un circuito sample-and-hold, che aumenta la complessità e gli errori analogici.[6]

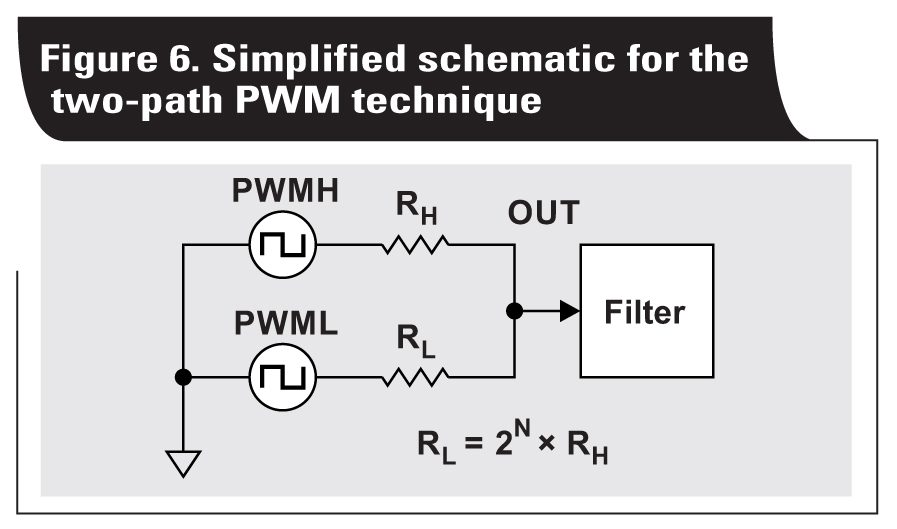

Una tecnica PWM a due vie è abbastanza semplice e può produrre risultati eccellenti.[7] La Figura 6 mostra un concetto semplificato di questa tecnica. Due output PWM: PWMH rappresenta gli N bit più significativi, mentre PWML rappresenta gli N bit meno significativi. Lo scaling delle resistenze (RHe RL) attenua la PWM meno significativa per generare un output a piccoli passi. RHe RLformano un separatore di potenziale ed è possibile utilizzare il metodo di sovrapposizione per calcolare l’output effettivo.

Figura 5. Confronto fra ENOB e larghezza di banda relativa per diversi valori N ed m

Figura 6. Schema semplificato per la tecnica PWM a due vie

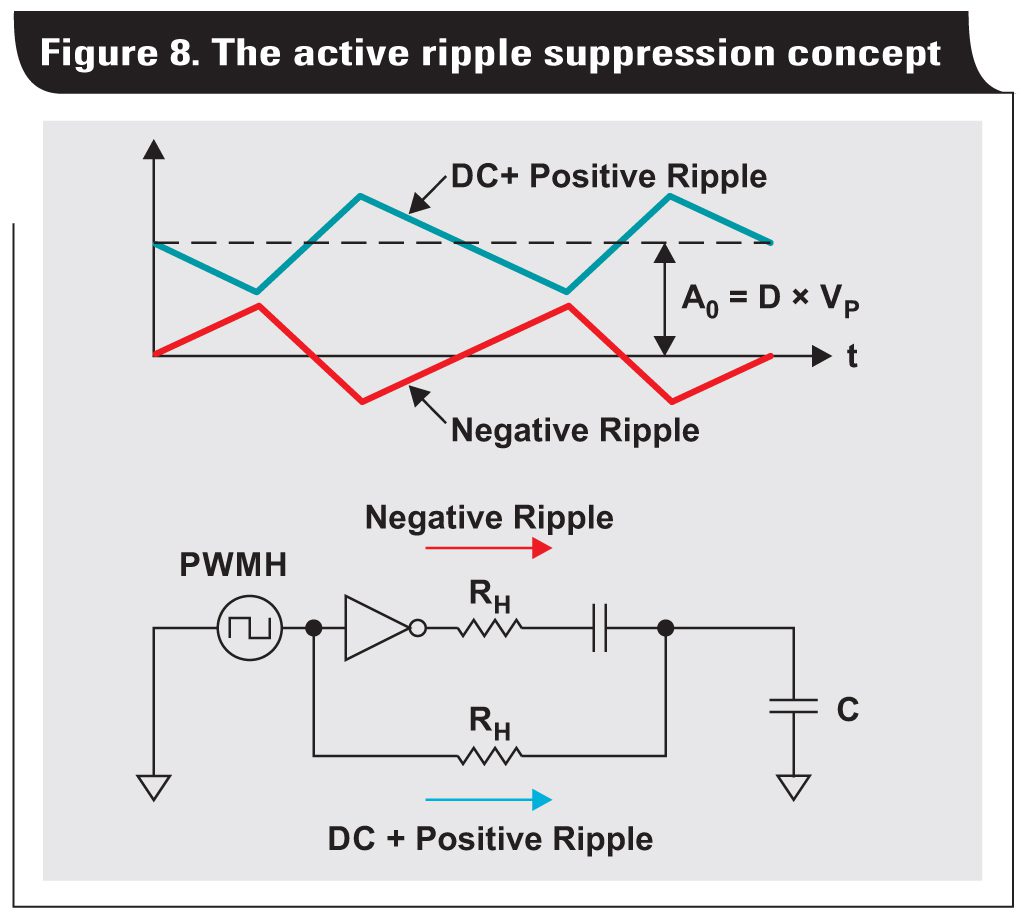

Nel dominio della frequenza, l’output di ogni input PWM viene trattato separatamente. Le Equazioni 15 e 16 esprimono rispettivamente le componenti CC di entrambi i segnali high e low.

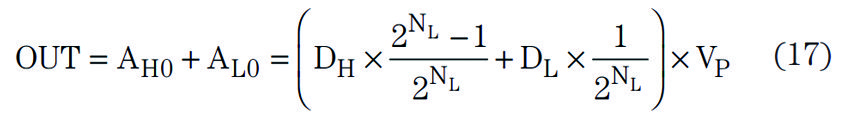

dove i pedici H ed L si riferiscono rispettivamente a PWMH e PWML. Supponendo che sia PWMH che PWML funzionino alla stessa frequenza, abbiano la stessa grandezza picco-picco e la stessa risoluzione, dove N = NL = NH, l’output può essere definito sommando le Equazioni 15 e 16, come nell’Equazione 17.

L’Equazione 18 calcola l’incertezza totale allo stesso modo.

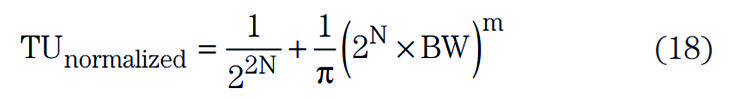

La magia della tecnica a due vie appare più ovvia se si confronta il diagramma ENOB con il diagramma della larghezza di banda relativa in Figura 7. Il raggiungimento di 16 bit di risoluzione su quasi 1 kHz di larghezza di banda (ipotizzando un clock di 16 MHz) è possibile semplicemente utilizzando un secondo output PWM a 8 bit e due resistenze di precisione.

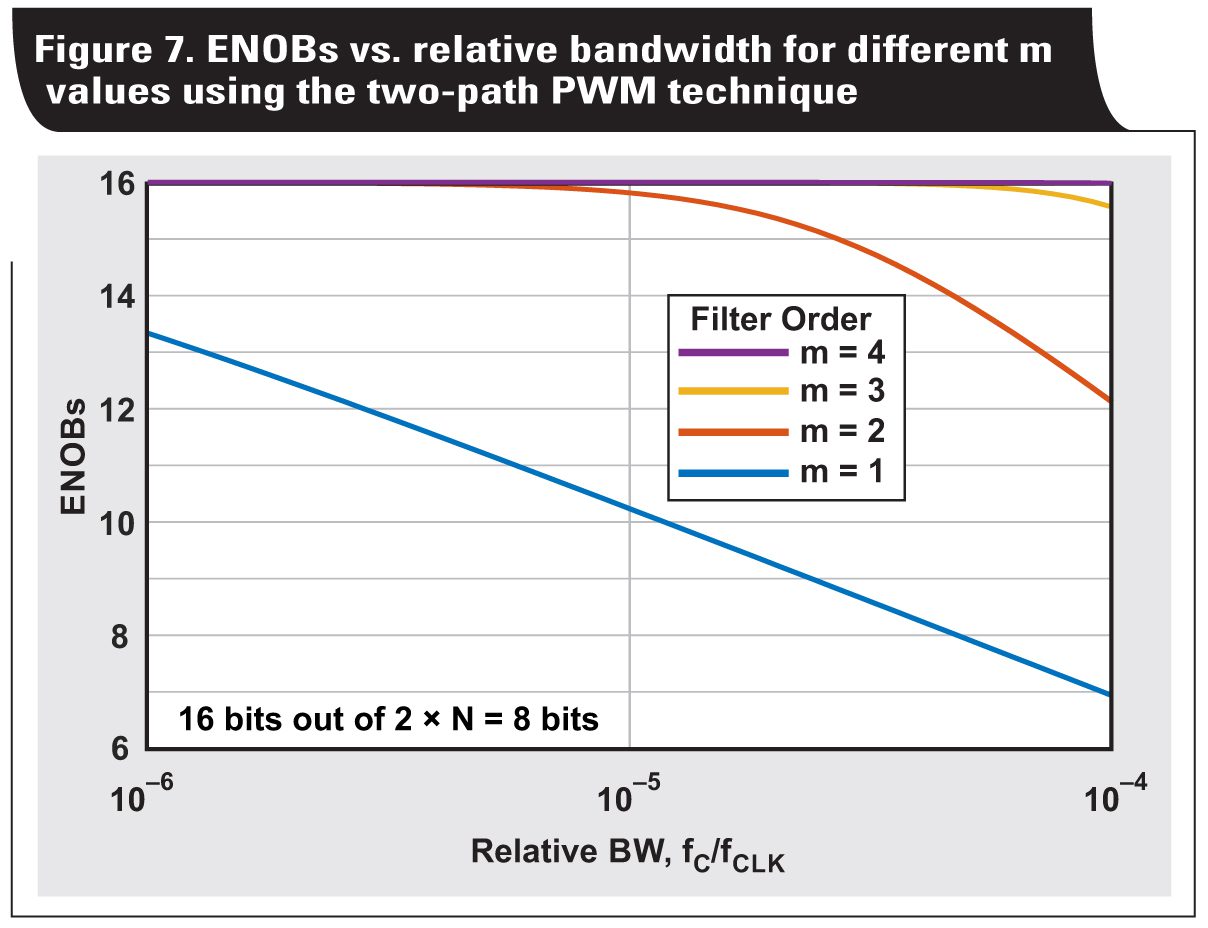

Soppressione attiva delle ondulazioni

Sebbene la tecnica PWM a due vie aiuti ad ottenere una risoluzione più elevata, l’ondulazione nel caso peggiore continua ad essere correlata ai bit più significativi. La soppressione attiva dell’ondulazione è una tecnica utilizzata nei convertitori audio a PWM per ridurre i livelli di ondulazione. L’idea è di ottenere un passa-banda del segnale PWM invertito e filtrato per eliminare la CC. Sommando questo segnale invertito al segnale principale si eliminano le armoniche di ordine superiore indesiderate. La Figura 8 mostra questo concetto con l’esempio per una via, con un filtro di primo ordine.

L’effetto della soppressione attiva delle ondulazioni può essere spiegato nel dominio della frequenza come la somma delle componenti della serie di Fourier (come in Figura 3) con quelli equivalenti, ma con uno sfasamento di 180 gradi. I risultati della simulazione mostrano una soppressione delle ondulazioni di –20 dB, che equivale ad un polo aggiuntivo per il filtro.

Buffering dei segnali PWM

Poiché il valore del segnale PWM picco-picco appare direttamente nella risoluzione (Equazione 4), è altamente consigliabile far sì che questo valore sia il più stabile possibile. Questo valore è una combinazione dell’accuratezza della tensione di alimentazione e dell’accuratezza di tensione high e tensione low del driver. L’accuratezza e la stabilità di questi parametri sono scarse per gli input/output generici dell’MCU.

Una semplice soluzione consiste nel bufferizzare l’output PWM dell’MCU con gate logici ad alta velocità e a bassa potenza, che sarebbero necessari anche per invertire i segnali richiesti dalla soppressione attiva delle ondulazioni. L’alimentazione di gate logici con un riferimento di tensione stabile invece di un tipico dispositivo di alimentazione porta a generare un segnale molto preciso e stabile.

Figura 7. Confronto fra ENOB e larghezza di banda relativa per diversi valori m utilizzando la tecnica PWM a due vie

Figura 8. Il concetto di soppressione attiva delle ondulazioni

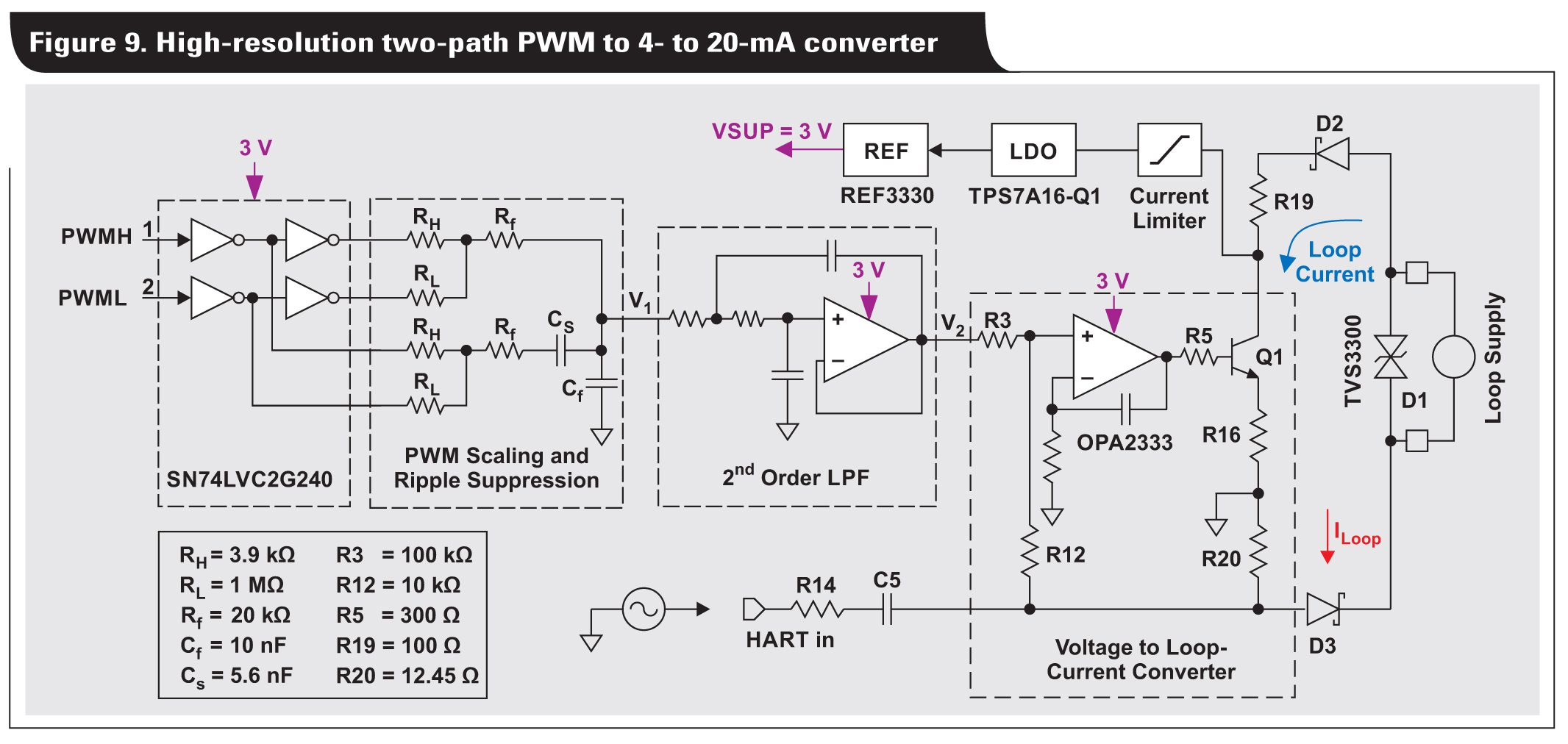

Schema del circuito

Il circuito in Figura 9 mostra un esempio dei concetti fin qui descritti: segnali PWM a due vie, bufferizzati con un riferimento di tensione come alimentazione, con soppressione dell’ondulazione tramite segnali invertiti. Lo stadio di soppressione delle ondulazioni con un filtro resistenza-condensatore (RC) di primo ordine fornisce una soppressione di –40 dB/decade delle ondulazioni PWM. Un filtro Sallen-Key attivo di secondo ordine segue per aggiungere altri due poli; pertanto il filtro effettivo complessivo è un filtro di quarto ordine. Il riferimento di tensione REF3330 a 3 V a bassa deriva alimenta i componenti attivi.

Un convertitore di corrente da 4 a 20 mA utilizza l’output del filtro (V2) come input, creando una corrente di loop espressa dall’Equazione 19.

Poiché V2 varia da 0 V a 3 V, l’intervallo di corrente del loop è compreso tra 0 mA e 24 mA. Per ulteriori dettagli sul trasmettitore loop e sui relativi calcoli, vedere il Riferimento 8.

Il trasmettitore è alimentato dal regolatore ad alta tensione e basso dropout (LDO) TPS7A16-Q1, che presenta un intervallo di ingresso da 3 V a 60 V. L’LDO genera 4,5 V di tensione intermedia per alimentare REF3330.

Figura 9. Convertitore da PWM a 4-20 mA a due vie ad alta risoluzione

Protezione

Per la protezione del loop, il posizionamento del diodo di soppressione della tensione transitoria bidirezionale (D1) TVS3300 33-V all’input del loop offre protezione dalle sovratensioni, mentre i diodi Schottky D2 e D3 proteggono dagli errori di cablaggio con inversione di ingresso, che potrebbero danneggiare l’LDO ad alta tensione. In caso di elevato carico capacitivo sui dispositivi di potenza, l’elevata corrente di spunto passa quindi alla massa locale fino alla resistenza di rilevamento R20, che potrebbe superare il limite di potenza di quella resistenza. L’aggiunta di un limitatore di corrente davanti all’LDO attenua la corrente di spunto. Per maggiori dettagli sulla progettazione del limitatore di corrente, vedere il Riferimento 9.

Tecniche a bassa potenza

Ottenere una bassa potenza, in particolare 100 μA per l’intero convertitore, era uno degli obiettivi per il circuito, ma richiedeva numerose tecniche di progettazione. La prima è stata utilizzare dispositivi a bassa corrente di quiescenza, tra cui LDO, riferimento di tensione e buffer logico, nonché l’amplificatore operazionale (in questo caso, OPA2333). L’utilizzo di RH = 3,9 kohm, più un 20 kohm più elevato per il filtro RC di primo ordine, costituisce una buona pratica in quanto i valori di resistenza, in particolare RH, svolgono un ruolo importante nella potenza dinamica tampone. La potenza rimanente viene consumata in R3, quindi R12, quindi Q1 del convertitore di corrente. Per ottenere la massima potenza, permettendo R3 = 100 kohm si assorbono 25 μA, mentre la base di Q1 assorbe 20 mA/r(Q1) nel peggiore dei casi. Per un tipico transistor a giunzione bipolare (BJT) dove r= 100, la corrente di base raggiungerebbe 200 μA, richiedendo un guadagno molto più elevato per il BJT. Una coppia di transistor, dove r= 104, riduce la corrente massima nella base Q1 a 2 μA.

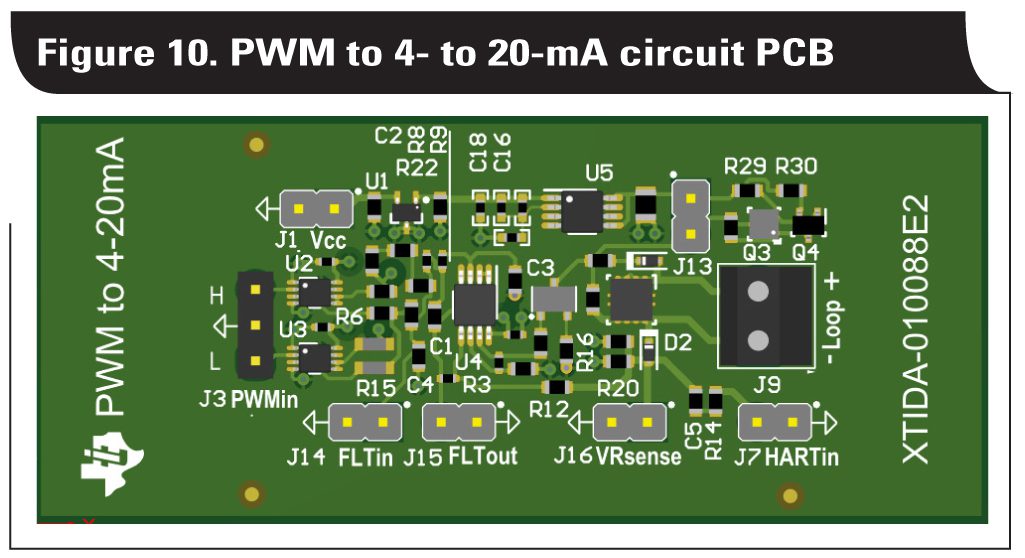

Il layout del circuito stampato (PCB) per il circuito mostrato in Figura 9. L’area PWM-tensione è di 15 mm x 7 mm.

I dispositivi di protezione sono 8 mm x 5 mm, mentre lo stadio di potenza è 13 mm x 3 mm. Sebbene l’impronta del circuito sia effettivamente minima, è possibile ridurla ulteriormente utilizzando package più piccoli della maggior parte dei dispositivi.

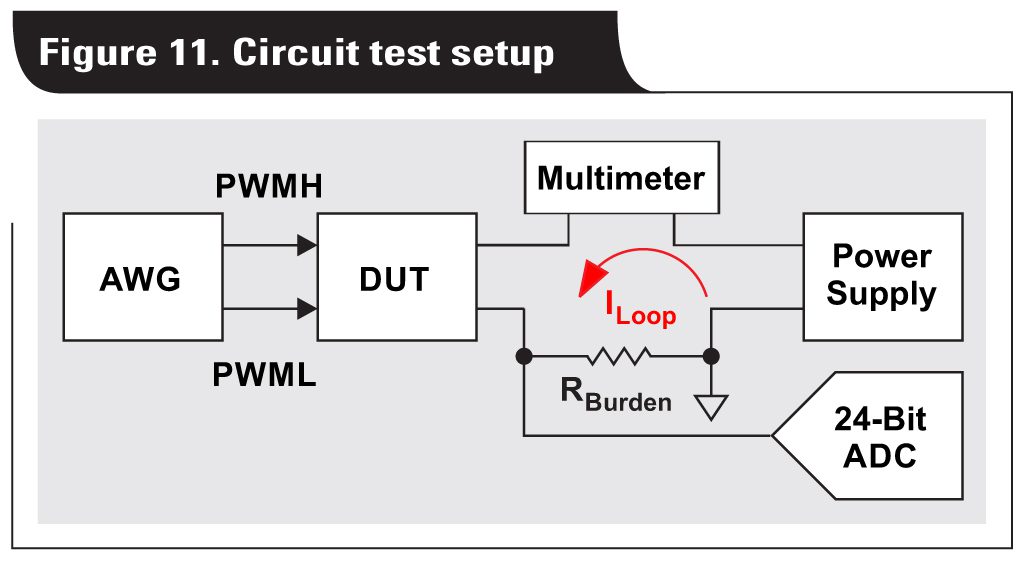

Configurazione di prova

La figura mostra la configurazione in cui è stato testato il circuito stampato.

Un generatore di forme d’onda analogico (AWG) con massa flottante genera i due segnali PWM. L’alimentatore fornisce l’alimentazione del loop. La corrente del loop viene misurata con un multimetro con risoluzione di 6,5 cifre nel corso di un singolo ciclo di alimentazione. Una resistenza di carico di precisione (RCarico) converte la corrente in tensione, mentre un ADC a 24 bit cattura il rumore di corrente non catturato altrimenti dal multimetro per via dell’averaging. Una sonda per oscilloscopio differenziale posizionata sul nodo PCB J15 (V2 nella Figura 9) misura il tempo di assestamento.

Risultati del test

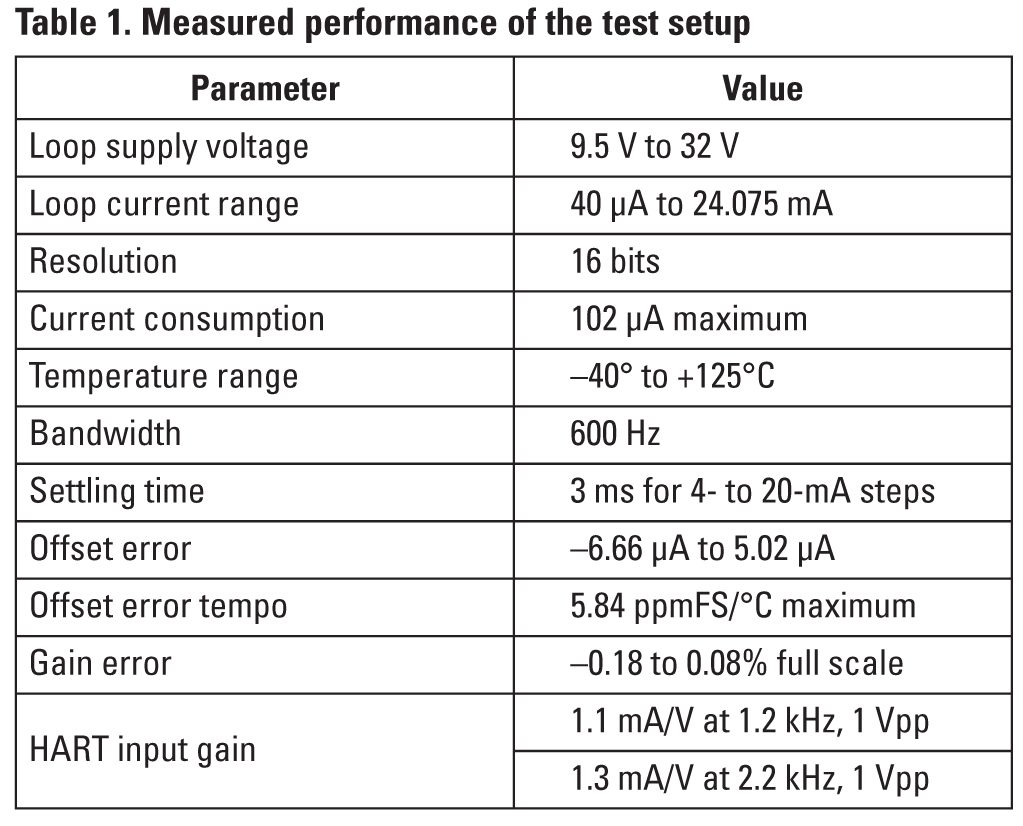

La Tabella elenca i risultati del test del circuito. Vedere il Riferimento 10 per maggiori dettagli sui risultati e sui grafici di misurazione.

Conclusione

Un’esplorazione della limitazione della classica tecnica PWM con DAC attraverso l’analisi matematica ha dimostrato che un progetto di convertitore da PWM a 4-20 mA che utilizza un riferimento di tensione e la soppressione attiva delle ondulazioni può ridurre il rumore fino a quasi lo 0,1% FS. Utilizzando una tecnica scalata a due vie si ottiene una risoluzione di 16 bit su una larghezza di banda di 600 Hz. Gli amplificatori a bassa potenza, i regolatori a bassa corrente di quiescenza e una coppia di transistor di uscita portano la potenza a un massimo di 102 μA sulla temperatura. Gli amplificatori presentano inoltre una deriva termica molto bassa, che produce piccoli errori di offset e prestazioni stabili su tutto l’intervallo di temperatura industriale.

[/boris]