Non ci sono prodotti a carrello.

Chi progetta con dispositivi ‘System-on-Chip’ programmabili ha spesso bisogno di molto supporto per arrivare a realizzare prototipi hardware funzionanti. Il concetto di System-On-Module (SOM) di Avnet supera le principali difficoltà dell’integrazione di sistema, grazie a una soluzione flessibile di gestione dell’alimentazione sviluppata espressamente da Infineon per rispondere alle necessità dei più moderni FPGA e SoC programmabili.

Introduzione: velocizzare lo sviluppo con SoC programmabili

I dispositivi System-on-Chip (SoC) programmabili possono contribuire ad accelerare lo sviluppo di nuovi prodotti, riducendo le dimensioni e il consumo energetico di una grande varietà di apparati che richiedono prestazioni di elaborazione avanzate e brevi tempi di risposta. Tipici esempi comprendono azionamenti motori ad alte prestazioni, sistemi di comunicazione, sistemi di visione e piattaforme per reti neurali (machine-learning).

Sviluppare un sistema basato su un SoC programmabile è tutt’altro che semplice e comporta sfide impegnative come la progettazione del layout del PCB. Disegnare linee di segnale ad alta velocità, integrare le memorie di sistema e interfacce come ethernet o USB, e in particolare gestire correttamente l’alimentazione è diventato molto complesso, perché ogni nuova generazione di SoC programmabili integra un numero crescente di funzioni e pone requisiti di sistema sempre più stringenti.

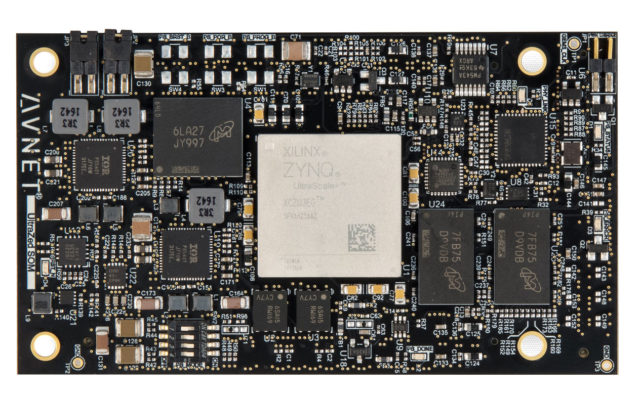

Un System-On-Module (SOM) contenente un completo sistema di elaborazione embedded basato su un SoC programmabile può aiutare a superare le sfide dello sviluppo e del debug del sistema, e consente ai progettisti del prodotto di ottenere rapidamente una piattaforma funzionante per sviluppare la configurazione del SoC in parallelo alla loro applicazione. Il System-On-Module “UltraZed-EG” di Avnet (figura 1) e i progetti di riferimento ad esso associati – tra cui schede carrier per specifiche applicazioni – sono innovativi in questo approccio allo sviluppo di sistemi basati su SoC programmabili. Inserendo il SOM nella scheda carrier si ottiene una piattaforma hardware pronta all’uso che può abbreviare il tempo di sviluppo e debug del sistema fino al cinquanta per cento.

Figura 1. SOM “UltraZED-EG” di Avnet, per accelerare lo sviluppo di sistemi basati su SoC programmabili ad alta integrazione.

Questo System-On-Module contiene una Zynq Ultrascale+ XCZU3EG MPSoC di Xilinx. Questo dispositivo è un tipico esempio della più recente generazione di SoC programmabili ad alta integrazione ed alte prestazioni, che combina un dispositivo FPGA evoluto con un sistema di elaborazione multi-core, memoria integrata ad alta velocità e interfacce di comunicazione multi-gigabit. Utilizzato sulla UltraZED-EG di Avnet o in una convenzionale scheda di prototipazione FPGA, questo dispositivo pone numerose sfide sul piano dell’alimentazione poiché integra molte risorse hardware.

Sfide nella gestione dell’alimentazione

Gli odierni SoC programmabili richiedono molteplici rail di alimentazione con diversi valori di tensione. Oltre alla tensione del core, il sistema di elaborazione della Zynq possiede domini di alimentazione separati per la memoria integrata, gli I/O, i circuiti PLL (Phase-Locked Loop) e i transceiver Multi Gigabit (SerDes). Inoltre bisogna tenere in considerazione le diverse modalità di funzionamento del dispositivo, come ad esempio: “sempre acceso” (always-on) o basso consumo. A seconda del dispositivo utilizzato possono essere necessari da sette a dieci diversi rail di alimentazione, e tutti devono essere accesi e spenti nella giusta sequenza. Infineon ha sviluppato e reso disponibili soluzioni per l’alimentazione delle Zynq UltraScale+ di Xilinx, dalle ZU02 alle ZU19, collaborando con Xilinx sull’ottimizzazione dei rail di alimentazione come descritto in Xilinx UG583 UltraScale Architecture PCB Design, e Infineon Power Solutions for Xilinx Zynq UltraScale+ MPSoC, nelle sezioni “Always On: Cost Optimized Power Rail Consolidation” e “Always On: Power/Efficiency Rail Consolidation for Low Power Devices”. Infineon è presente su numerosi reference designs con Avnet e Xilinx per l’intera famiglia Zynq UltraScale+.

Le specifiche riguardanti la precisione della tensione DC e la risposta al gradino di carico sono molto stringenti. La tensione che alimenta il core dei dispositivi Zynq UltraScale+ deve avere una precisione dell’1%, con un ripple picco-picco inferiore a 10 mV. Inoltre, poiché i dispositivi sono realizzati con processi avanzati come la tecnologia FinFET a 16 nm di Xilinx, questo alto livello di precisione è necessario con tensioni fino a 0,72 V.

Molto stringenti sono anche le specifiche della precisione AC in risposta al gradino di carico. Xilinx richiede che undershoot e overshoot di tensione restino contenuti entro il 3% del valore nominale per transienti fino al 30% della corrente di carico. Per dispositivi piccoli come le famiglie da ZU02 a ZU05, la corrente di picco del core è compresa tra 7 A e 16 A, mentre un MPSoC Zynq di grandi dimensioni come il dispositivo ZU19 può assorbire correnti fino a 40 A. Sono inoltre necessari ulteriori rail per pilotare altri circuiti con domini di alimentazione separati, come il codec video integrato nei dispositivi Zynq della serie EV. La tensione del rail che alimenta il core deve restare entro il 3% del valore nominale per variazioni della richiesta di corrente compresi tra i due terzi del pieno carico e il valore di picco. In un dispositivo ZU19, ciò equivale a un gradino che sale da 25 A a 40 A.

I dispositivi Zynq UltraScale+ integrano anche dei blocchi SerDes su pin di I/O disponibili all’utente, per facilitare un’efficiente conversione tra i protocolli seriali ad alta velocità, utilizzati all’esterno del chip, in bus paralleli più adatti ad essere gestiti dalle IP interne e dalla logica del SoC. Questi blocchi SerDes possono rimanere inutilizzati se non necessari, ma se attivati richiedono ulteriori rail di alimentazione e impongono requisiti ancora più stringenti sulla risposta al gradino di carico. I transceiver SerDes possono consumare fino a 20 W a seconda del loro numero e del tipo di dispositivo. Possono funzionare a velocità comprese tra 1,5 Gbit/s e 80 Gbit/s e il ringing picco-picco sulla loro alimentazione deve essere contenuto entro i 10 mV.

Come se progettare un alimentatore capace di rispondere a tutti questi requisiti non fosse già abbastanza complicato, occorre anche una certa flessibilità per far fronte a eventuali modifiche o ridimensionamenti del progetto nel corso dello sviluppo. Se si sceglie di utilizzare un diverso SoC, anche il numero dei rail e la potenza consumata cambieranno – in una misura che dipende dal particolare dispositivo prescelto e dalle risorse utilizzate nell’ambito del dispositivo stesso. E ovviamente i circuiti di alimentazione devono occupare poco spazio, per sfruttare al meglio i vantaggi dimensionali resi possibili dall’alto livello di integrazione del SoC.

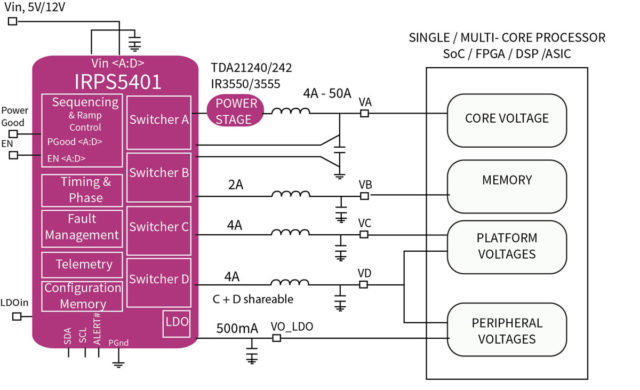

Per il proprio SOM UltraZED-EG, Avnet ha scelto di utilizzare due PMIC (Power-Management IC) IRPS5401 di Infineon. Ogni PMIC integra cinque convertitori DC/DC e un regolatore LDO (figura 2). Per fornire ulteriore flessibilità e consentire l’alimentazione di core che assorbono correnti fino a 40 A, uno dei convertitori DC/DC offre anche un’uscita PWM che può essere utilizzata per pilotare uno stadio di potenza esterno, come il circuito integrato TDA21240 sempre di Infineon.

Figura 2. Esempio di configurazione dell’IRPS5401 per alimentare un SoC programmabile.

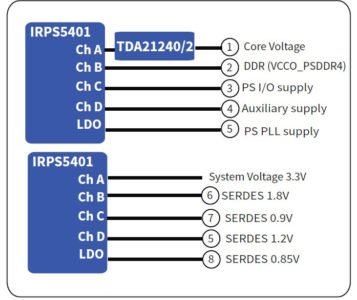

Per aiutare i progettisti ad accelerare la realizzazione dei loro alimentatori, Infineon ha sviluppato dodici configurazioni di IRPS5401 pronte all’uso, specificamente rivolte all’alimentazione dei dispositivi Zynq UltraScale+. Oltre a rispondere ai diversi requisiti dei vari membri della famiglia Zynq, queste configurazioni tengono conto anche delle opzioni disponibili: le modalità “sempre acceso” o a basso consumo, i SerDes attivati o non attivati. Per semplificare ulteriormente il progetto, Infineon ha preparato un manuale (Power Cookbook) che fornisce ai progettisti tutto ciò di cui hanno bisogno per individuare la configurazione adatta al dispositivo Zynq prescelto e ottenere tutti gli elementi per implementarla, compresi gli schemi elettrici e i file gerber. La figura 3 mostra una delle configurazioni illustrate nel Power Cookbook, che impiega i due PMIC per generare tutti i rail di alimentazione necessari per Zynq UltraScale+, compresi quelli per i blocchi SerDes.

Figura 3. Due dispositivi IRPS5401 costituiscono la soluzione ad alta integrazione per generare i vari domini di alimentazione richiesti dalla Zynq e dai suoi blocchi SerDes.

Il PMIC IRPS5401 semplifica anche la programmazione delle corrette sequenze di accensione e spegnimento, un risultato difficile da ottenere se si progetta l’alimentatore partendo da zero. Il dispositivo, infatti, può essere programmato rapidamente tramite l’interfaccia grafica “PowIRCenter” di Infineon. Il ritardo dopo l’accensione o lo spegnimento e i tempi di salita e discesa di ciascun rail vengono programmati scrivendo i relativi valori con l’interfaccia grafica (figura 4).

Figura 4. L’interfaccia grafica PowIRCenter viene utilizzata per definire le corrette sequenze di attivazione dei rail di alimentazione.

Programmare la sequenza di accensione e spegnimento sfruttando le funzioni dell’IRPS5401 è molto più semplice e veloce che progettare circuiti di temporizzazione per ogni singolo rail, come occorrerebbe fare nell’ambito di un progetto di alimentatore sviluppato a discreti. La funzione di sequencing è incorporata nel PMIC, pertanto non occorrono né un microcontrollore esterno né un timer dedicato, il che consente di ridurre lo spazio occupato sulla scheda e il costo della BOM. Il PMIC IRPS5401 contiene anche registri e circuiti analogici integrati per realizzare la funzione di margining della tensione, senza necessità di componenti esterni. I progettisti possono specificare i limiti adeguati e svolgere test sui margini, sempre operando tramite la GUI PowIRCenter.

PowIRCenter facilita anche il debugging della scheda basata sul SoC, sfruttando il fatto che IRPS5401 può utilizzare l’intero set dei comandi PMBus 1.2. Questo semplifica notevolmente il compito del progettista nella fase di verifica delle prime schede prodotte, permettendo il monitoraggio di aspetti quali potenza d’ingresso, potenza d’uscita, tensione d’uscita, sovracorrenti, sensori di temperatura e indicatori di guasti. Il monitoraggio in tempo reale dello stato dell’alimentatore, tramite l’interfaccia PMBus del PMIC, può essere sfruttato, ad esempio, per un indicatore di ‘alimentazione OK’ in apparati come i server per l’elaborazione video, oppure per inviare dati prestazionali al cloud per l’analisi.

Alimentazione scalabile per i SoC programmabili

Infineon ha progettato l’IRPS5401 per fornire una soluzione scalabile alle esigenze di alimentazione di FPGA e SoC programmabili di diversi produttori. Questo PMIC può semplificare la gestione dell’alimentazione per una varietà di sistemi basati sui dispositivi Zynq della gamma compresa tra la serie più semplice, ZU2, e la serie ad alte prestazioni, ZU19. Questa gamma comprende la linea dei prodotti base Zynq CG, dotati di un processore dual-core ARM Cortex-A53; i dispositivi a maggiori prestazioni Zynq EG, con processore quad-core Cortex-A53 e processore grafico Mali-400; e la linea dei prodotti Zynq EV, dotati di Cortex-A53 quad-core, Mali-400 e codec video H.264/H.265 integrato.

La SOM UltraZED-EG di Avnet, che contiene un singolo dispositivo Zynq ZU03-EG, sfrutta l’alta integrazione e flessibilità dell’IRPS5401 per ottenere dimensioni compatte: solo 3,5 pollici (76,2 mm) x 2 pollici (50,8 mm). Questa stessa flessibilità può essere sfruttata dagli utilizzatori per affinare lo schema di alimentazione tramite PowIRCenter, al fine di soddisfare le specifiche necessità delle loro applicazioni man mano che il progetto si sviluppa. Ciò può evitare settimane o mesi di ‘prove ed errori’, una fase altrimenti necessaria per ottimizzare un alimentatore convenzionale.

Conclusioni

Gli odierni dispositivi FPGA ad alte performance e i SoC programmabili più avanzati dimostrano la tendenza al continuo aumento della densità e delle funzioni integrate – caratteristiche che richiedono un maggior numero di rail di alimentazione, valori di correnti più alti su ogni rail, ma anche una maggiore precisione DC e migliori prestazioni della risposta ai transienti. Il crescente impiego di questi dispositivi rende più importanti gli aspetti che, a livello di sistema, incidono sui tempi di sviluppo del prodotto e sulle dimensioni della scheda, es.: la densità di potenza, il sequencing dei rail, la telemetria e la scalabilità dell’infrastruttura di alimentazione. Progettare un alimentatore che risponda a tutti questi requisiti è un compito complesso e impegnativo che può appesantire notevolmente il lavoro degli sviluppatori.

Un PMIC configurabile progettato espressamente per alimentare queste categorie di dispositivi costituisce una soluzione flessibile e scalabile al problema. Questa soluzione ha rappresentato il fattore abilitante per la realizzazione del System-On-Module UltraZED-EG di Avnet, il modulo finalizzato a semplificare lo sviluppo di nuovi prodotti basati sul dispositivo Zynq UltraScale+ di Xilinx.

A Cura di Udo Blaga, Avnet Silica, e Tony Ochoa, Infineon.

1 Commento