Non ci sono prodotti a carrello.

L’avvento della guida autonoma, delle automobili connesse e dei veicoli elettrici/veicoli elettrici ibridi sta cambiando i paradigmi nel settore automobilistico. La sicurezza funzionale, fondamentale per queste tecnologie, non si limita più ai microcontroller tradizionali (MCU), ma deve essere supportata anche nei processori applicativi. I requisiti di calcolo delle centraline dei motori (ECU) sono in crescita e alla base della necessità di processori più versatili, acceleratori hardware e processori di segnale digitale (DSP) per soddisfare i bisogni applicativi. Tenendo conto di questi parametri, diventa più impegnativo per i core già esistenti elaborare i dati relativi alla sicurezza e disporre di funzioni a criticità mista. I sistemi a criticità mista eseguono operazioni con diversi livelli di criticità su una piattaforma condivisa. Nei sistemi a criticità mista è necessario garantire rigorosamente la tempestività delle operazioni critiche per la sicurezza.

La famiglia di system-on-chip (SoC) Jacinto™ 7 di TI per l’automotive non si limita a integrare una MCU di sicurezza ASIL-D isolata, ma offre anche livelli superiori di sicurezza funzionale ASIL per tutti i core di elaborazione. In questo white paper verranno analizzati i sistemi diagnostici di sicurezza integrati nella famiglia di SoC Jacinto 7, che comprende i dispositivi TDA4x e DRA8x, i vari meccanismi di isolamento disponibili per supportare un sistema a criticità mista, l’architettura software, le proposte per i prodotti software e come costruire una soluzione completa.

Che cos’è la sicurezza funzionale?

La sicurezza funzionale è la capacità di un sistema di reagire ai malfunzionamenti, che si tratti di un guasto casuale, di un guasto hardware o di stress ambientali, in modo tale da minimizzare il danno. Come previsto dalla norma ISO 26262, ciò significa semplicemente la libertà da un rischio non accettabile. Sebbene il concetto di sicurezza funzionale sia noto nell’industria automobilistica da parecchio tempo, la sua adozione nei processori applicativi è appena agli inizi. Tenendo a mente le applicazioni conformi ad ASIL-D, i processori Jacinto 7 introducono concetti di sicurezza che un tempo erano limitati a dispositivi di classe MCU per i processori applicativi.

Questi processori utilizzano tecniche di isolamento con assistenza hardware che rendono possibile realizzare sistemi a criticità mista. La capacità di ospitare, senza soluzione di continuità, operazioni sia critiche sia non critiche per la sicurezza su uno stesso dispositivo aiuta a ridurre i costi di sistema.

La famiglia di processori Jacinto 7 offre una soluzione di sicurezza completa che comprende sia l’hardware che il software. È progettata sistematicamente per funzionalità ASIL-D utilizzando un processo di sviluppo hardware certificato da un ente esaminatore della sicurezza funzionale indipendente, come il TÜV SÜD. Dotata di circuiti diagnostici in grado di rilevare guasti casuali, può essere suddivisa in tre ampie categorie:

- Diagnostica fondamentale, che copre i circuiti di test per memoria, clock, alimentazione, core e interconnessioni.

- Funzionalità di isolamento hardware, come tensione/alimentazione/reset separati, firewall, unità di gestione della memoria (MMU) e microprocessori (MPU), che facilitano la Freedom From Interference (FFI) in sistemi che supportano operazioni a criticità mista (es.: ASIL-B e ASIL-D).

- Diagnostica hardware specifica dell’applicazione come il rilevamento del fermo immagine.

La famiglia di processori Jacinto 7, inoltre, verrà certificata esternamente come elemento di sistema fuori contesto per il livello ASIL richiesto dall’apparecchiatura terminale di destinazione. Come il processo di sviluppo hardware, anche il processo di sviluppo software è certificato da un ente esaminatore della sicurezza funzionale indipendente, come il TÜV SÜD. I componenti software Jacinto 7 che dispongono di requisiti di sicurezza sono progettati per supportare requisiti di sicurezza funzionale fino al livello ASIL-D. I componenti software non sono certificati esternamente. Un pacchetto di supporto per la certificazione permette di certificare il proprio software/sistema finale. Le librerie di diagnostica software vengono fornite con esempi di utilizzo della diagnostica su chip. TI offre certificati di sicurezza funzionale per hardware e software compatibili.

Una delle differenze fondamentali nell’architettura di sicurezza dei processori Jacinto 7 è l’integrazione di funzionalità MCU che semplificano la progettazione dei sistemi, riducono il numero di componenti sulla scheda e lo spazio. Il processore applicativo è diviso in due domini indipendenti: il dominio principale e il dominio MCU. Il dominio principale presenta core per il calcolo ad alte prestazioni, come una MPU e un’unità di elaborazione grafica (GPU), acceleratori multimediali e per la visione, inclusi i DSP, nonché le necessarie periferiche. Il dominio MCU è un dominio indipendente per le funzioni di sicurezza con elevata FFI.

I processori Jacinto 7 sono dispositivi conformi alla sicurezza muniti di documentazione per la sicurezza funzionale costituita da:

- Un manuale di sicurezza, che fornisce informazioni per agevolare la creazione di un sistema critico per la sicurezza utilizzando una famiglia di processori Jacinto 7 supportata. Questo documento contiene dettagli sul processo di sviluppo, sull’architettura di sicurezza funzionale e sui meccanismi di sicurezza funzionale implementati.

- Una relazione di analisi della sicurezza, contenenti informazioni sulla capacità del dispositivo di raggiungere gli obiettivi di sicurezza funzionale stabiliti.

- Un’analisi quantitativa della sicurezza funzionale (nota anche come Failure Mode, Effects and Diagnostic Analysis, FMEDA) fa anch’essa parte della relazione di analisi della sicurezza, ma costituisce un documento a parte. Essa contiene dettagli sulle diverse parti del componente ed è idonea per consentire calcoli basati su un’applicazione personalizzata dei meccanismi di sicurezza funzionale della diagnostica, oltre a contenere informazioni su FIT, copertura diagnostica, SPFM/LFM e modalità di guasto.

Panoramica della sicurezza funzionale software

Il software è un elemento importante per raggiungere l’obiettivo di sicurezza complessivo di un prodotto. Per il software Jacinto 7 la sicurezza è costituita da questi due aspetti:

- Funzionalità sistematiche dei componenti software utilizzati nel percorso di sicurezza.

- Supporto software completo per la diagnostica hardware e codice di esempio di riferimento.

Per le funzionalità sistematiche, TI segue un processo di sviluppo software comune ben definito e strumenti condivisi dai vari team. Un’organizzazione indipendente per la qualità del software è responsabile per l’approvazione di tutti i prodotti software. I deliverable di sicurezza funzionale di TI includono:

- Conformità del processo: il processo di sviluppo del software di sicurezza funzionale è certificato dal TÜV SÜD per ISO 26262 per ASIL-D e IEC 61508.

- Conformità del progetto: la conformità del progetto è garantita mediante verifica interna e nel rispetto dei processi ISO 26262 o IEC 61508. Ogni non conformità viene corretta mediante piano e azioni di miglioramento.

- Certificazione abilitante per il cliente: tutto il software sviluppato con l’impiego del processo di sicurezza è fornito con un Compliance Support Package (CSP). Il CSP include:

- Una relazione di verifica interna di TI.

- Requisiti, un piano di test e report.

- Un report di tracciabilità.

- Un report di analisi della copertura di codice dinamico.

- Un report di analisi del codice statico/report della Motor Industry Software Reliability Association-C.

- Una libreria e un manuale di diagnostica per la sicurezza funzionale.

- Un kit di qualifica per compilatore.

- Un report di analisi della modalità di guasto e degli effetti software.

Il kit di sviluppo software Jacinto 7 unificato (SDK) fornisce inoltre supporto software che permette di creare la propria soluzione di sicurezza. I componenti che devono essere utilizzati in un sistema «as is» e che fanno parte di un circuito di sicurezza sono sviluppati secondo il processo di sviluppo software per sicurezza funzionale di TI. Il processo comprende una libreria diagnostica software per tutti gli IP di sicurezza fondamentali e software funzionale come driver per il livello di astrazione microcontroller, IPC e DMA.

Inoltre, TI fornisce vari esempi di riferimento per aiutare a capire come utilizzare queste funzionalità di sicurezza nelle proprie applicazioni. Poiché le funzionalità di sicurezza possono variare da un’applicazione a un’altra, il software di riferimento non è sviluppato utilizzando il processo di sicurezza, ma segue invece il processo baseline di TI.

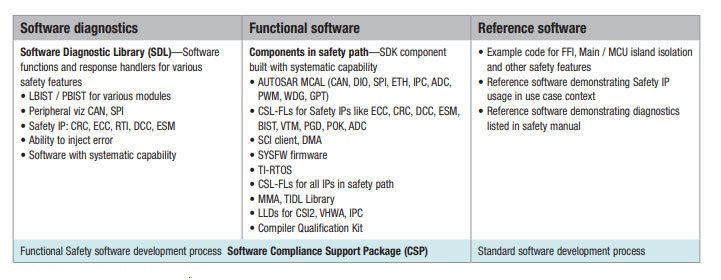

La Tabella 1 mostra vari esempi di quanto viene fornito nel software di diagnostica, nel software funzionale e nel software di riferimento che sono inclusi nel SDK.

Mappatura dell’applicazione di sicurezza

Le tipiche architetture SoC create per data center e applicazioni mobili sono sprovviste delle funzionalità di sicurezza necessarie per le applicazioni automotive e, a loro volta, richiedono ulteriori prestazioni di calcolo per l’aggiunta di diagnostica di sicurezza basata su software. Le varie funzionalità di sicurezza hardware e software della famiglia di processori Jacinto 7, se utilizzate in un’applicazione finale, possono aiutare a ridurre le prestazioni di calcolo necessarie.

Tabella 1. Proposte di sicurezza funzionale software.

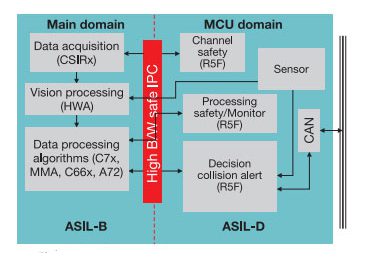

La Figura 1 alla pagina seguente mostra un tipico sistema basato sulla visione. I dati in ingresso dalla telecamera sono acquisiti tramite Camera Serial Interface e sono inviati ad un motore hardware di elaborazione della visione per la conversione da dati grezzi a YUV. Vari algoritmi analitici e di deep learning, come la classificazione degli oggetti e il rilevamento di spazio libero, vengono eseguiti sui core on-chip C7x DSP, MMA e Arm® Cortex®-A72 del processore. Il dominio MCU funge da controllo per ogni passaggio e, periodicamente, provvede alla convalida e al monitoraggio dei dati in elaborazione. Il dominio MCU, inoltre, assume le decisioni finali delle funzioni di sicurezza sulla base di altri input dei sensori, che sono quindi comunicati ad altre ECU automotive attraverso un protocollo di comunicazione come Controller Area Network (CAN).

Figura 1. Tipica elaborazione della visione.

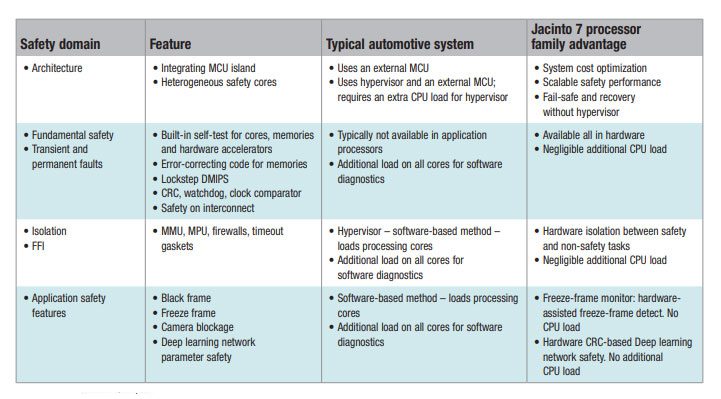

Ciascuno dei blocchi nella Figura 1 rappresenta moduli sul processore Jacinto 7 e comprende diagnostica hardware per soddisfare l’obiettivo di sicurezza complessivo senza utilizzare le risorse della CPU. La Tabella 2 mappa la stessa applicazione di visione a cui si è fatto riferimento in precedenza e mostra la differenziazione della sicurezza funzionale fra la famiglia di processori Jacinto 7 e un SoC tipico.

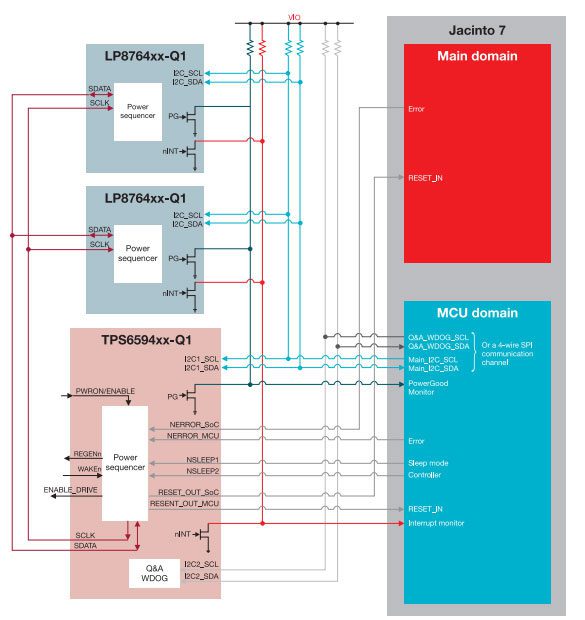

Soluzioni di gestione dell’alimentazione compatibili con processori Jacinto

Parallelamente alla famiglia di processori Jacinto, TI ha sviluppato due circuiti PMIC (Power Management Integrated Circuits) flessibili e ad alta precisione, idonei per applicazioni automotive che richiedono sicurezza funzionale e muniti di documentazione per la sicurezza funzionale. Questi PMIC, TPS6594-Q1 e LP8764-Q1, offrono una soluzione di gestione scalabile della potenza sia per il dominio principale sia per il dominio MCU e supportano la sicurezza funzionale fino a ASIL-D.

Tabella 2. Mappatura della sicurezza per le applicazioni.

Un sistema dall’architettura corretta supporta i requisiti di sicurezza funzionale, tra cui:

- Il SoC controlla i dati dei sensori

- La MCU controlla il SoC

- La MCU controlla gli attuatori

- La MCU controlla che gli attuatori reagiscano al comando nel modo previsto

- Il PMIC monitora l’esecuzione hardware e software della MCU

- Il PMIC monitora il funzionamento hardware del processore applicativo

Se il PMIC rileva un funzionamento errato, mette il sistema in uno stato sicuro forzando il pin di uscita ENDRV su low. Esempi di errori sono:

- Guasti nelle tensioni di alimentazione della MCU o del SoC

- Guasto nella tensione di alimentazione di ingresso verso i PMIC

- Errore del software o hardware della MCU

- Errore hardware dell’SoC segnalato dall’ESM per il SoC

I dispositivi TPS6594-Q1 e LP8764-Q1 possono essere utilizzati come PMIC indipendenti, ma, in sistemi in cui si utilizzano più PMIC per la scalabilità con un processore o una MCU, i PMIC comunicano fra loro attraverso un’interfaccia a due fili coperta mediante protocollo CRC. L’interfaccia consente di sincronizzare gli stati di alimentazione e la gestione degli errori fra i PMIC. L’interrogazione periodica del bus permette di verificare lo stato di salute di tutti i PMIC sul bus di comunicazione. Questa implementazione garantisce una rapida risposta alle condizioni di guasto del sistema e, pertanto, permette alla soluzione di puntare ad obiettivi di sicurezza funzionale superiori per il sistema finale. La Figura 2 mostra un esempio di collegamento fra due PMIC e un caso d’uso di un sistema con processore Jacinto 7. La maggior parte delle applicazioni utilizza un solo TPS6594-Q1, ma l’impiego di un ulteriore LP8764-Q1 permette di sopportare funzionalità di sistema aggiuntive. Questa possibilità di utilizzare uno o più PMIC per alimentare il SoC attraverso un PMIC «virtuale» permette di ottimizzare i costi di sistema nei casi d’uso che richiedono meno potenza, consentendo al tempo stesso le massime prestazioni possibili dei sistemi.

Figura 2. Comunicazione TPS6594-Q1 + LP8764-Q1 + LP8764-Q1 come PMIC «virtuale»

La nuova famiglia di processori Jacinto 7 di TI con caratteristiche di sicurezza funzionale integrate su chip permette ai clienti di conseguire meglio la certificazione di sicurezza e raggiungere gli obiettivi per i propri prodotti finali. Le vaste funzionalità di sicurezza aiutano a ridurre la BOM del sistema e possono ridurre l’eccesso di prestazioni sui diversi core. Inoltre, il SDK del software TI fornisce driver relativi alla sicurezza e librerie diagnostiche per aiutare i clienti a raggiungere i propri obiettivi di sviluppo per il software di sicurezza. Un’architettura di sicurezza semplificata e le proposte software possono aiutare i clienti a ridurre notevolmente l’impegno nello sviluppo ingegneristico.

Risorse supplementari

- Kumar, VC. «The state of functional safety in Industry 4.0». White paper Texas Instruments SPRY329, 2018.

- Thomas, Jay e Siddharth Deshpande. «Foundational Software for Functional Safety». White paper Texas Instruments SPNY007, 2015.

- Certificato hardware di sicurezza funzionale.

- Certificato software di sicurezza funzionale.

- Chitnis, Kedar, et al. «Enabling Functional Safety ASIL Compliance for Autonomous Driving Software Systems». Electronic Imaging, Autonomous Vehicles and Machines 2017, Society for Imaging Science and Technology (29 gennaio 2017), pagg. 35–40.

- Haworth, David, Tobias Jordan e Alexander Much. «Freedom from Interference from AUTOSAR-Based ECUs: A Partitioned AUTOSAR Stack». Automotive – Safety & Security, LNI 210 (2012), pagg. 85–98.

A cura di: Yashwant Dutt, Engineering Manager Jacinto™ Processors; Sam Visalli, Functional Safety Manager Jacinto Processors; Mahmut Cifti, Systems Architect Jacinto Processors; Dave Maples, General Manager Automotive Gateway and Infotainment Jacinto Processors; Krishna Gopalakrishnan, Quality Manager Embedded Processing Texas Instruments.