Non ci sono prodotti a carrello.

Le larghezze di banda dei circuiti in ambito aerospace and defence e di test and measurements di prossima generazione si stanno spostando da 10 a 100 sec di megahertz e da multigigahertz a larghezze di banda istantanee. Le tendenze nei radar phase-array, nei sistemi di test wireless 5G, nella guerra elettronica e negli oscilloscopi digitali stanno spingendo le larghezze di banda sempre più in alto, aumentando anche il numero di canali di ciascun sistema.

Queste tendenze rendono più complessa la progettazione della catena del segnale, incluso il convertitore ADC, il clock e l’alimentazione. La selezione di un appropriato convertitore dati, la sincronizzazione di più canali e l’ottimizzazione dell’alimentazione sono fondamentali per ottenere la larghezza di banda necessaria su più canali.

Selezione del convertitore di dati

Ogni architettura di sistema inizia con il dispositivo che influisce maggiormente sulle prestazioni del sistema; nei sistemi a banda larga, questo è il convertitore dati (ADC). La sua selezione dipende dalle tue risposte alle seguenti domande:

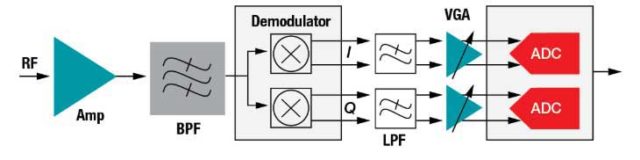

Utilizzerai un’architettura a frequenza intermedia (IF) zero / architettura mixer complessa (Figura 1)?

- Pro: la larghezza di banda di ingresso del convertitore da analogico a digitale (ADC) e le frequenze di campionamento sono inferiori rispetto ad altre architetture ed è possibile semplificare o eliminare il filtraggio.

- Contro: sono necessari due canali ADC per elemento antenna per i percorsi I e Q con l’immagine del mixer può ridurre le prestazioni del sistema.

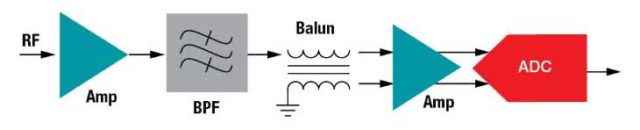

Userete un approccio eterodina (Figura 2)?

- Pro: è necessario un solo canale di conversione dati e la larghezza di banda di ingresso ADC è inferiore al campionamento a radiofrequenza (RF).

- Contro: richiede uno o più mixer, l’immagine del segnale e le armoniche generate complicheranno il filtraggio, ed è difficile regolare la frequenza di interesse; è necessario spostare l’oscillatore locale (LO).

Utilizzerai il campionamento RF diretto (Figura 3)?

- Pro: data la catena del segnale semplificata, non è necessario un mixer ed è facile adattare la frequenza in modo digitale utilizzando convertitori Digital Down Converter (DDC) e gli oscillatori a controllo numerico (NCO).

- Contro: la frequenza del segnale più alta deve essere all’interno della larghezza di banda di ingresso dell’ADC e sarà necessario pianificare la frequenza per ottenere le massime prestazioni.

Figura 1: tipica architettura mixer complessa

Figura 2: tipica architettura eterodina

Figura 3: tipica architettura di campionamento RF

Qual è il segnale di larghezza di banda più ampio che devi misurare?

- Come minimo, il convertitore di dati avrà bisogno di una frequenza di campionamento di almeno 2,5 volte la larghezza di banda istantanea del segnale per il campionamento diretto o di 1,25 volte per zero IF.

- Per prestazioni ottimali, una frequenza di campionamento di circa 10 volte la larghezza di banda istantanea consentirà di evitare più facilmente armoniche e spurie.

Il tool RF-sampling frequency planner, analog filter and DDC Excel calculator può aiutare nella scelta dei componenti in funzione dei requisiti di sistema e mostrare gli effetti sul complesso campionamento digitale del segnale.

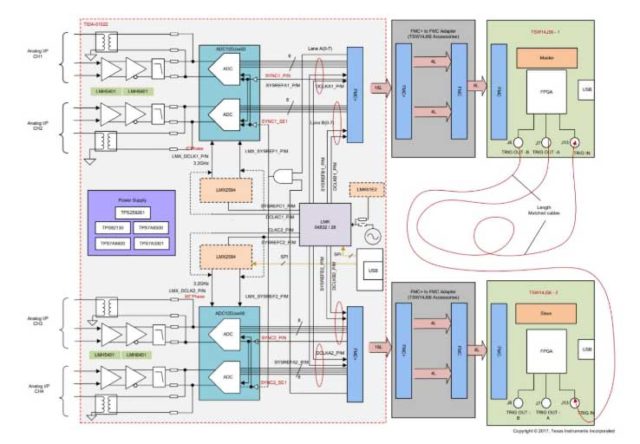

Come accennato in precedenza, i sistemi a banda larga richiedono convertitori con una elevata frequenza di campionamento. Ad esempio, un sistema di campionamento RF con una larghezza di banda del segnale di 1 GHz trarrebbe vantaggio da un convertitore dati con una velocità di conversione di circa 10 Gsps al fine di evitare armoniche di segnale. Fino a poco tempo fa, il convertitore più veloce di TI era l’ ADC12DJ3200 che è un ADC a 12 bit che funziona a 3,2 Gsps per canale in modalità a doppio canale o 6,4 Gsps in modalità a canale singolo. Ma anche in modalità a canale singolo, non soddisfa la velocità desiderata di 10 Gsps. Quindi, per soddisfare questo requisito, il Flexible 3.2 GSPS Multichannel AFE Reference Design for DSOs, RADAR and 5G Wireless Test Systems, mostrato in Figura 4, combina due ADC12DJ3200 su una scheda.

Figura 4: diagramma a blocchi del design di riferimento AFE multicanale

Questo design di riferimento offre flessibilità di sistema, poiché può funzionare in modalità quad-channel, 3.2-Gsps, dual-channel, 6.4-Gsps o come singolo canale con un massimo di 12,8 Gsps. Il design di riferimento front-end analogico 12,8 GSPS per oscilloscopio ad alta velocità e digitalizzatore a banda larga illustra l’interlacciamento a bordo dei due ADC.

Con la recente introduzione del nuovo ADC12DJ5200RF 5.2-Gsps a doppio canale, è possibile incrementare prestazioni e flessibilità per i progetti di prossima generazione. Poiché l’ADC12DJ5200RF è compatibile pin-to-pin con l’ADC12DJ3200, è possibile modificare rapidamente il progetto di riferimento e garantire un design di riferimento scalabile da 20,8 Gsps per digitalizzatori a 12 bit. A 20,8 Gsps, l’intera larghezza di banda di ingresso a 8 GHz del dispositivo può essere digitalizzata in un’unica acquisizione.

È tempo di clock

Dopo aver selezionato il convertitore è ora di progettare l’architettura del clock. Il clock di un singolo convertitore dati è semplice, ma molti sistemi, come il nostro design interlacciato, devono sincronizzare molti convertitori come avviene, ad esempio, nei sistemi phased-array che possono utilizzare centinaia o migliaia di canali. TI ha diversi dispositivi e progetti di riferimento per affrontare questi complessi progetti.

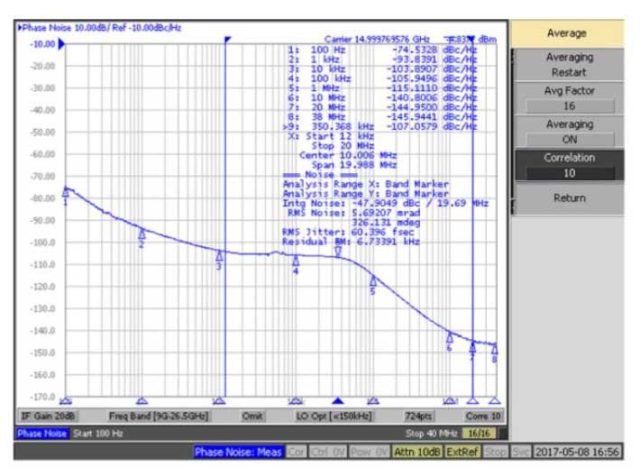

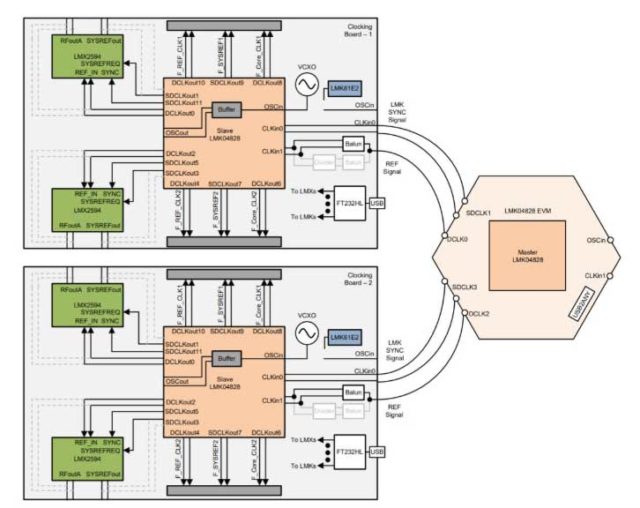

Il design di riferimento di clock multicanale JESD204B a 15 GHz per tester wireless DSO, radar e 5G è un sottosistema di clock completo. Il circuito, visibile in Figura 5, include più opzioni di clock come l’oscillatore programmabile LMK61E2 e l’LMK04828, un dispositivo di distribuzione del clock con 14 uscite di clock indipendenti, così come il sintetizzatore phase-locked loops LMX2594 che forniscono un bassissimo segnale di rumore in fase fino a 15 GHz, come mostrato in Figura 6. Inoltre, l’LMX2594 può anche generare un segnale di clock sincronizzato SYSREF per ADC con interfaccia JESD204B. Il LMX2594 dà anche la possibilità di sincronizzare la fase di vari segnali di clock attraverso dispositivi multipli. Il progetto di riferimento fornisce anche grafici del rumore di fase a più frequenze, come mostrato in Figura 6, e anche misurazioni del ritardo da canale a canale (skew) con ritardi inferiori a 10 ps.

Figura 5: diagramma a blocchi di clock multicanale JESD204B a 15 GHz.

Figura 6: rumore di fase dell’LMX2594 a 15 GHz

Come configurata, la scheda supporta fino a due ADC e due FPGA, ma può essere facilmente adattata per sincronizzare fino a sei convertitori e un FPGA. Tuttavia, altri sistemi richiedono molti più canali. Per queste situazioni, il nostro design di riferimento di generazione di clock JESD204B ad alto numero di canali per i tester wireless RADAR e 5G e il design di riferimento di clock daisy chain JESD204B ad alto numero di canali per i tester wireless RADAR e 5G consentono il funzionamento dei nostri sistemi in una struttura ad albero, mostrata in Figura 7, o in una configurazione daisy chain. Utilizzando queste tecniche, è possibile espandere il sistema a migliaia di canali con un degrado minimo delle prestazioni.

Figura 7: JESD204B diagramma a blocchi del generatore di clock con struttura ad albero

Alimentare il circuito

Una volta risolta l’architettura di sincronizzazione, la sfida successiva riguarda l’alimentazione. I convertitori e i generatori di clock possono essere sensibili al rumore di commutazione dei convertitori DC/DC, quindi la maggior parte dei progettisti farà ricorso a convertitori DC/DC a basso rumore e bassa caduta di tensione, tipicamente un LDO. Tuttavia, con un layout particolarmente accurato e con dei filtri adeguati, su prodotti di consumo è anche possibile fare a meno degli LDO.

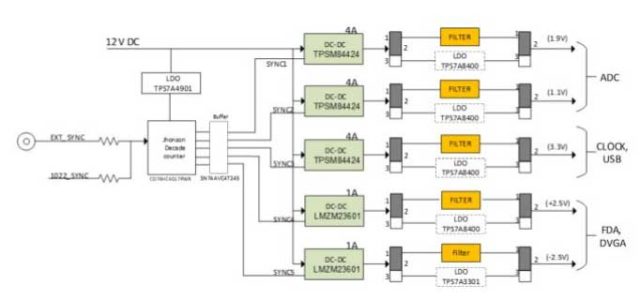

Il design di riferimento front-end analogico multicanale 3.2-Gsps visto in precedenza utilizza un alimentatore completo, inclusi regolatori DC/DC e LDO, come mostrato in Figura 8. Gli LDO su questo design possono essere bypassati con specifici filtri per testare quali sono gli alimentatori più sensibile al rumore di commutazione. I nostri test hanno confermato che non vi è alcun impatto sulle prestazioni del progetto bypassando gli LDO, il che offre anche il vantaggio aggiuntivo di una maggiore efficienza dell’alimentazione.

Figura 8: schema a blocchi dell’alimentatore per il design di riferimento AFE multicanale 3.2-Gsps

La scheda include anche una serie di pin di intestazione nella parte superiore che consentono di bypassare la soluzione di alimentazione di bordo con un nuovo design, come il nostro design di riferimento dell’alimentatore a basso rumore che massimizza le prestazioni nei sistemi di acquisizione dati 12,8 Gsps. Questo progetto di riferimento, mostrato in Figura 9, consente la sincronizzazione di tutti i regolatori DC/DC con un clock master, facilitando il filtraggio del rumore di commutazione del convertitore. Inoltre, è possibile spostare la fase del clock di ciascun convertitore in modo che tutti i convertitori non si trovino a commutare contemporaneamente, riducendo l’energia complessiva assorbita. Infine, i convertitori DC/DC nel progetto di riferimento sono più efficienti, contenendo la perdita di potenza totale sulla scheda. Come per il design originale, anche in questo caso gli LDO possono essere bypassati.

Figura 9: Design di riferimento a blocchi del circuito di alimentazione a basso rumore

In ultima analisi la sfida progettuale non riguarda solo la conversione dei dati ma anche i circuiti di clock e di alimentazione che possono influire sulle prestazioni complessive del sistema.

Risorse addizionali

- Guarda il video: Optimize Your RF Sampling ADC Receiver Performance with the Frequency and Sample Rate Planning Calculator.

- Scopri i portafogli di convertitori ADC ad alta velocità e convertitore da digitale ad analogico di TI .