Non ci sono prodotti a carrello.

Di Thomas Neu, System Engineer per convertitori di dati ad alta velocità

Introduzione

I progetti tradizionali per l’acquisizione di dati industriali richiedono spesso filtri elaborati sul front-end analogico (AFE) a monte del convertitore analogico/digitale (ADC). L’obiettivo principale di un filtro analogico è attenuare i segnali fuori banda indesiderati che possono introdurre alias al di sopra del segnale di interesse desiderato: pertanto, il filtro analogico è noto anche come filtro anti-alias (AAF). Segnali e rumore indesiderati nella banda di alias possono provenire dall’amplificatore di azionamento, da spurie di commutazione dell’alimentatore o anche da interferenze intenzionali (jammer).

La posizione della frequenza di alias dipende direttamente dalla frequenza di campionamento dell’ADC: più il convertitore di dati funziona velocemente per una determinata larghezza di banda istantanea, più la banda di alias si allontana dal segnale desiderato e più diventa facile il filtraggio. Nei sistemi ad altissima precisione, i progettisti sfruttano spesso questa relazione utilizzando ADC delta-sigma, che per progetto utilizzano tassi di sovracampionamento elevati insieme a filtri di decimazione. Nelle stazioni base dei cellulari, la spinta al campionamento diretto in radiofrequenza delle bande 3GPP da 1 a 6 GHz ha portato all’adozione di convertitori di dati gigasample-per-second (GSPS). La larghezza di banda istantanea delle bande 3GPP è solo una frazione della frequenza di campionamento, pertanto la nuova architettura di utilizzo del convertitore GSPS con sovracampionamento ha anche ridotto i requisiti per il filtro RF analogico.

Le applicazioni industriali che utilizzano ADC a registro di approssimazione successiva (SAR), come l’analisi della qualità dell’energia, il sonar o il radar industriale con frequenze di campionamento comprese tra 1 MSPS e più di 10 MSPS, si collocano tra l’ADC delta-sigma di precisione e l’ADC GSPS. Le nuove famiglie ADC35xx e ADC36xx di ADC SAR ad alta velocità sono abbinate ad un filtro digitale integrato, consentendo alle applicazioni industriali di sfruttare questa tecnica di progettazione a sovracampionamento e decimazione per ridurre i requisiti del filtro analogico esterno.

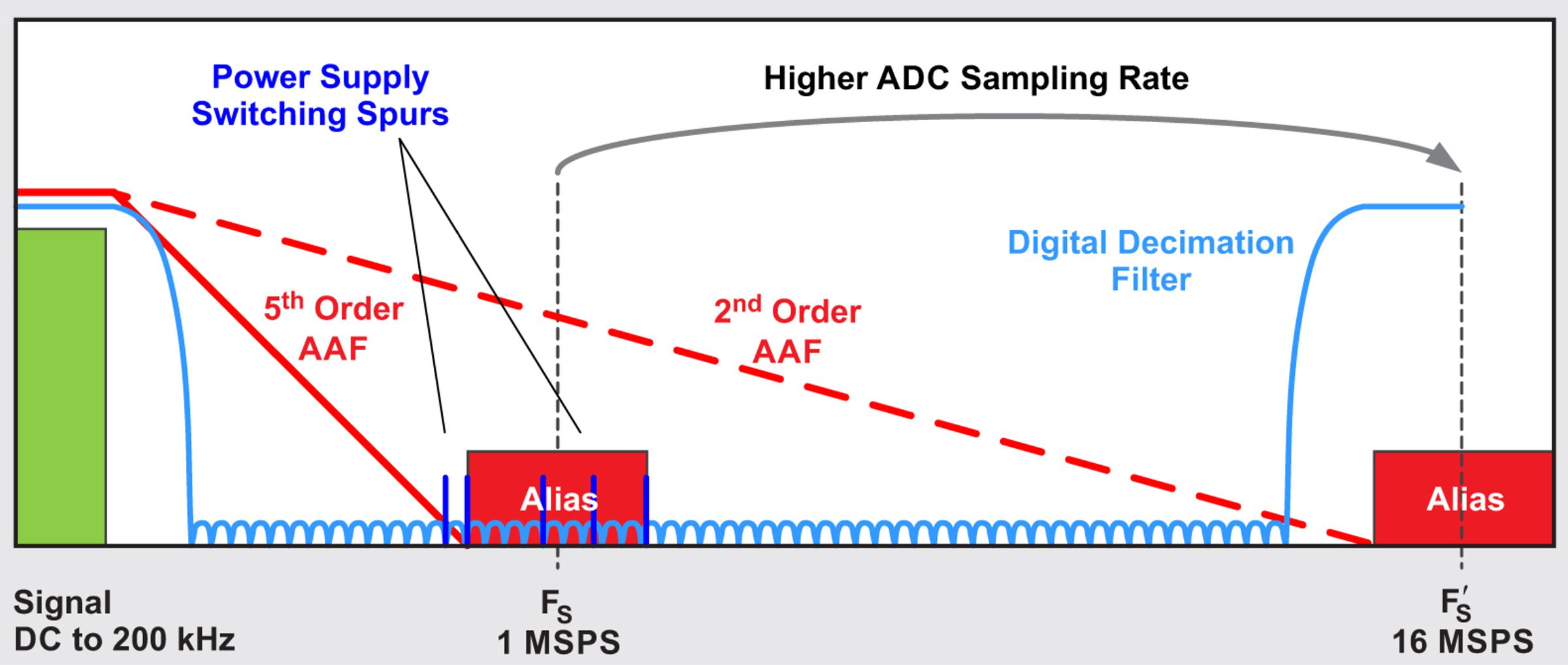

Per l’esempio mostrato nella Figura 1, si supponga che il segnale di ingresso CC sia 200 kHz con una frequenza di campionamento ADC di 1 MSPS. Una banda passante di circa 300 kHz insieme a una reiezione dell’alias di circa 40 dB richiede approssimativamente un filtro di quinto ordine. Aumentando la frequenza di campionamento dell’ADC da 1 MSPS a 16 MSPS, la banda di frequenza dell’alias viene spinta da 800 kHz a 15,8 MHz e, quindi, riduce il filtro anti-alias ad un filtro di secondo ordine. Inoltre, la banda di alias si allontana dalla regione di frequenza (da 600 kHz a 2 MHz), che spesso contiene spurie causate da regolatori di commutazione nell’alimentatore.

Figura 1. Rilassamento del filtro anti-alias dovuto all’aumento delle frequenze di campionamento dell’ADC

Filtro digitale interno

Il prossimo obiettivo è esaminare i tre scopi del filtro digitale interno.

1.Attenuazione della banda di frequenza alias

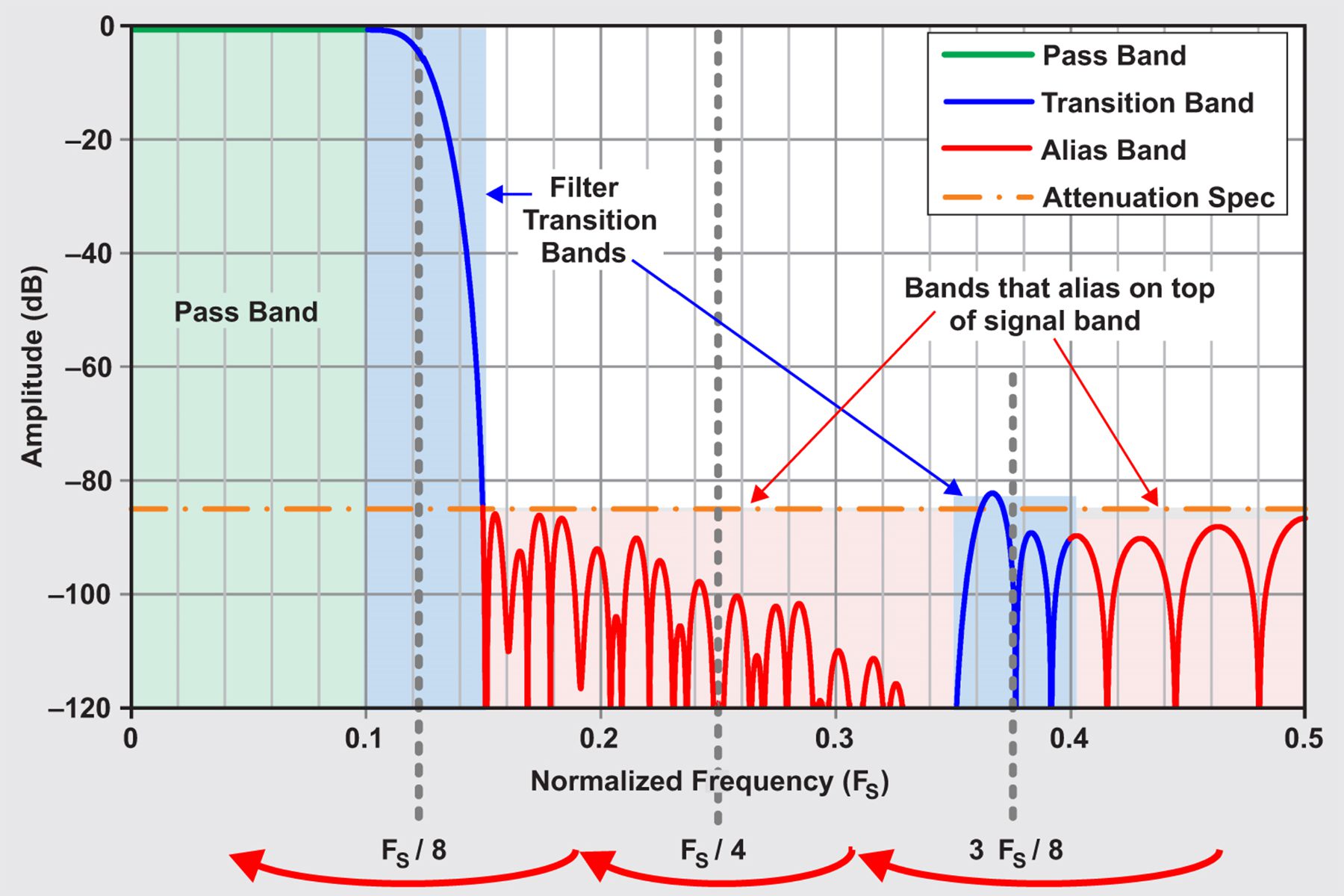

Il filtro di decimazione digitale più comune nel dominio della frequenza è un filtro passa-basso digitale. Questo filtro è costituito da tre diverse regioni: la banda passante, le bande di transizione multiple e le bande alias, come mostrato nella Figura 2. Tutti i segnali nelle bande alias diventano alias sopra la banda passante, ma risultano attenuati di circa 85 dB o più in questa figura. Tutte e tre le bande alias girano a specchio intorno a FS/8, FS/4 e 3 FS/8.

2.Riduzione della velocità dei dati in uscita

Un’elevata frequenza di sovracampionamento può essere difficile da gestire per i processori a valle. Inoltre, in una configurazione di sovracampionamento, la maggior parte dello spettro di frequenza contiene solo contenuti indesiderati, che consumano energia non necessaria per la trasmissione. Il filtro digitale scarta i campioni e riduce la velocità dei dati in uscita.

Quando la banda di interesse non è nella gamma di frequenza di fascia bassa, un mixer digitale può convertire il segnale prima del filtraggio passa-basso per massimizzare la riduzione della velocità di uscita.

3.Miglioramento del SNR

Il rapporto segnale-rumore (SNR) di un convertitore di dati viene calcolato integrando il rumore di fondo nella zona di Nyquist dell’ADC. In teoria, l’SNR dell’ADC migliora di 3 dB per ogni fattore di 2 decimazioni digitali. In realtà, è possibile avvicinarsi ai 3 dB fino a quando il rumore in banda inizia ad essere predominante.

Nell’esempio precedente, la frequenza di campionamento dell’ADC è aumentata da 1 MSPS a 16 MSPS. L’aggiunta di un filtro digitale decimato per 16 ridurrebbe la velocità di uscita a 1 MSPS, aumentando quindi l’SNR dell’ADC fino a 12 dB (4 × 3 dB).

La densità spettrale del rumore (NSD) è un’altra misura delle prestazioni di rumore del convertitore di dati e prende in considerazione l’SNR e la larghezza di banda, venendo spesso utilizzata per confrontare diversi convertitori di dati. Ad esempio, un ADC a 16 MSPS con un SNR di 82 dB avrebbe un NSD di –151 dBFS/Hz [82 dB 10 × LOG (8 MHz)]. Dopo la decimazione di un fattore 16, l’SNR migliora di 12 dB (da 82 a 94 dB), mentre l’NSD rimane costante a –151 dBFS/Hz [94 dB 10 × LOG (0,5 MHz)].

Capire il filtro di decimazione

Diversi compromessi determinano l’architettura del filtro digitale e il numero di prese del filtro: coefficienti programmabili o fissi, ondulazione massima della banda passante, attenuazione minima della banda di arresto, latenza e consumo energetico. Ad esempio, un più netto roll-off del filtro e una maggiore attenuazione della banda di arresto richiedono un numero maggiore di prese del filtro, con conseguente aumento del consumo energetico e maggiore latenza. I coefficienti del filtro determinano se il filtro fornisce una risposta in frequenza passa basso, passa alto o passa banda.

[boris]

Quando si integra un filtro digitale con un convertitore di dati ad alta velocità, un filtro passa-basso a mezza banda a risposta finita all’impulso (FIR) è utilizzato più comunemente dai progettisti di ADC perché la sua struttura è intrinsecamente molto efficiente dal punto di vista energetico. «Mezza banda» significa decimazione per 2; ogni due coefficienti, uno è zero e questi coefficienti non utilizzano alcuna potenza di calcolo. I coefficienti diversi da zero sono disposti simmetricamente attorno al centro della risposta all’impulso.

Figura 2. Regioni del filtro di decimazione nel dominio della frequenza

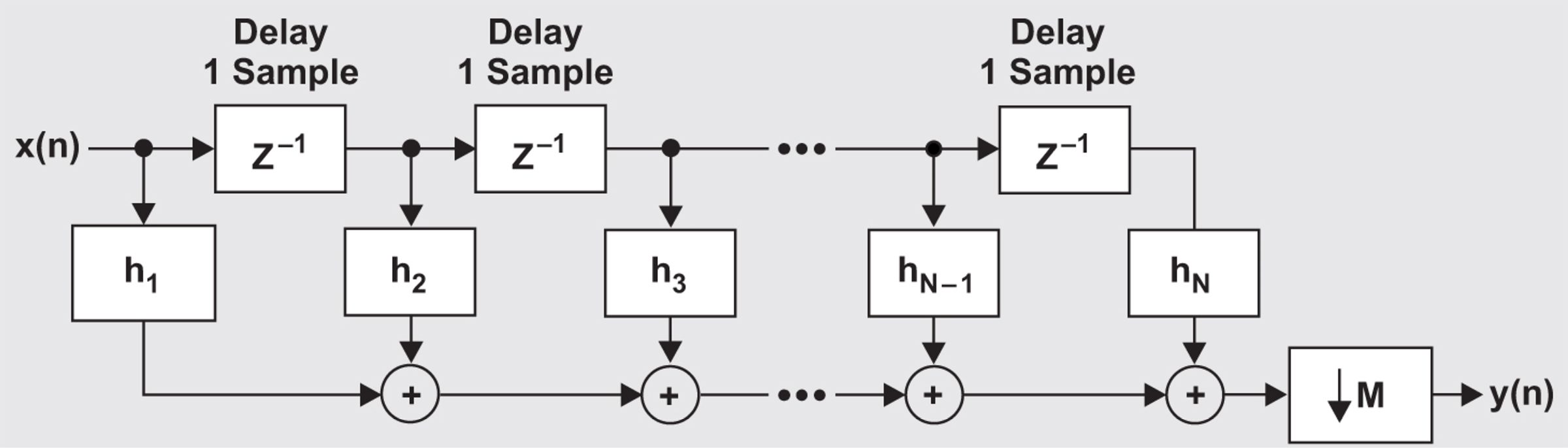

La Figura 3 mostra un’implementazione FIR generica. In un’implementazione a mezza banda con sette prese/coefficienti (N = 7), tutte le prese pari (h2, h6) tranne h4 sono zero, il che riduce le sette moltiplicazioni a cinque. Per velocità di decimazione più elevate, i filtri a mezza banda sono concatenati.

In teoria, un filtro passa-basso, passa-alto o passa-banda potrebbe essere integrato con l’ADC, tuttavia, un filtro passa-basso è la scelta più pratica, soprattutto quando si aggiunge un mixer complesso per costruire un sintonizzatore digitale.

Si noti che il filtro digitale si trova a valle della conversione da analogico a digitale. Pertanto, il filtro digitale non può impedire il jamming intenzionale o non intenzionale del ricevitore in cui l’ADC viene portato in saturazione. È importante continuare a utilizzare il filtraggio esterno e il guadagno regolabile per evitare di sovraccaricare l’ADC.

Figura 3. Esempio di implementazione di un progetto FIR

Decimazione complessa: sintonizzatore digitale

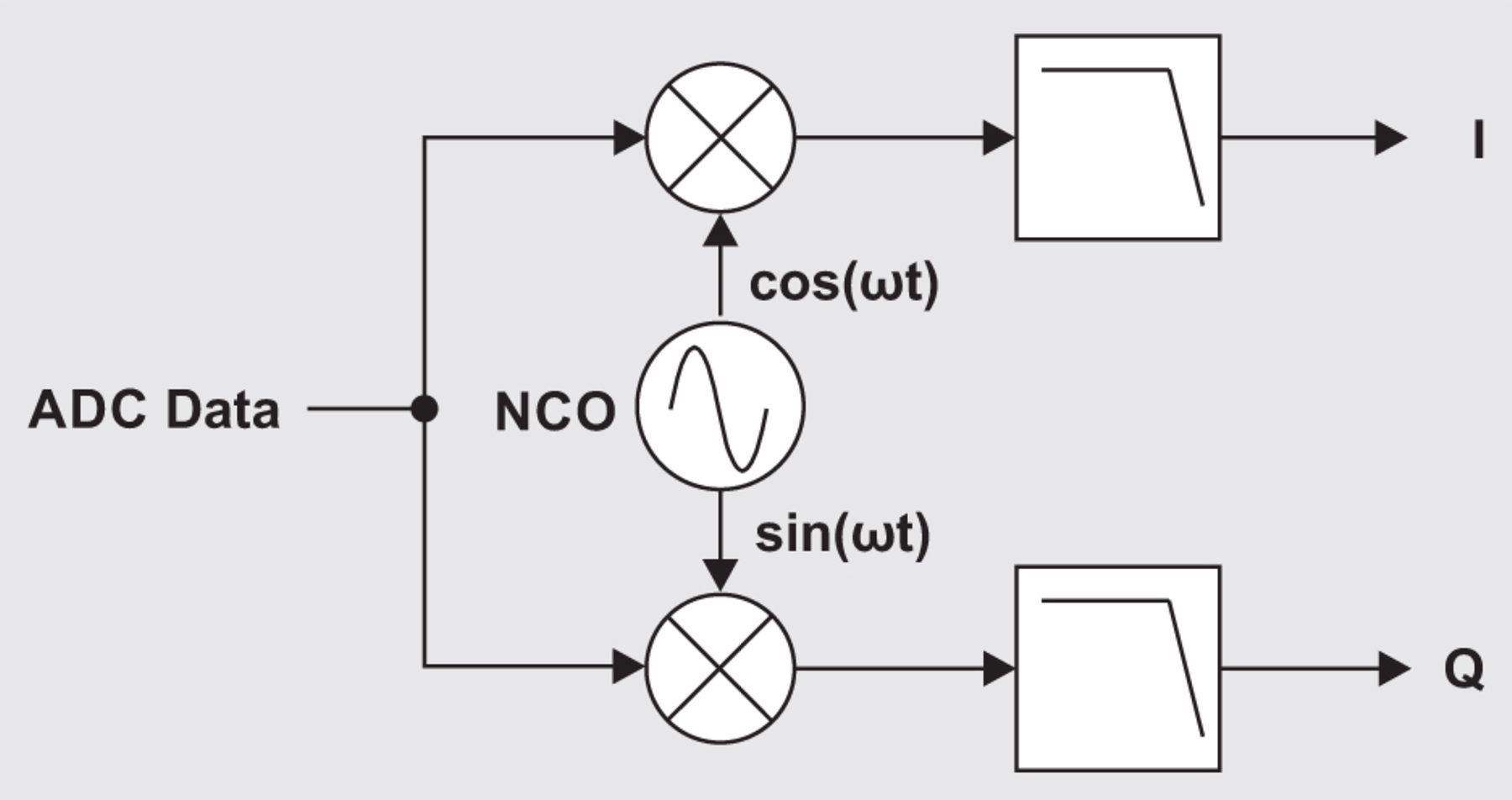

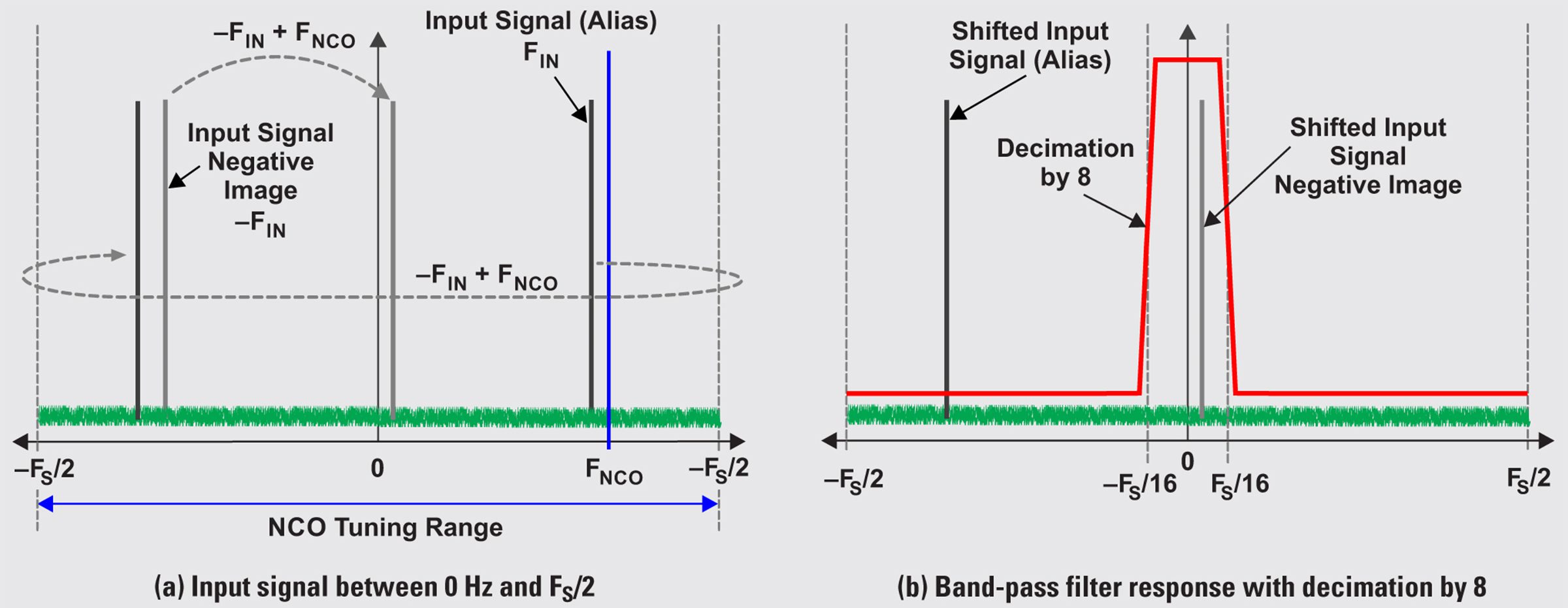

Aggiunta di un mixer complesso [utilizzando cos(ùt) e sin(ùt) per uscita I/Q] trasforma i due filtri passa-basso digitali in un filtro passa-banda digitale sintonizzabile, come si vede nella Figura 4. Il mixer utilizza un oscillatore a controllo numerico (NCO) come oscillatore locale (LO). Sia il percorso «I» che il percorso «Q» sono veri filtri passa-basso nel dominio della frequenza. La differenza di fase tra seno e coseno annulla le frequenze positive/negative. Il mixer digitale sposta qualsiasi frequenza all’interno della zona di Nyquist positiva o negativa a zero Hertz, creando quindi un filtro passa-banda sintonizzabile e molto potente, oltre a sostituire un mixer analogico tradizionale. La Figura 5 mostra il processo di sintonizzazione digitale. La zona di Nyquist dell’ADC mostra il segnale di ingresso (FIN) tra 0 Hz e FS / 2. L’immagine negativa di quel segnale in ingresso (–FIN) si trova tra 0 Hz e –FS / 2. Sia il segnale di ingresso che la sua immagine negativa sono miscelati con la frequenza NCO (+FNCO in questo esempio). +FIN ruota nella zona di Nyquist negativa mentre –FIN ruota nella zona di Nyquist positiva. L’esempio mostra una risposta del filtro passa-banda con decimazione per 8 centrata su 0 Hz, che passa la frequenza –FIN miscelata con la frequenza NCO (FOUT = –FIN + FNCO).

Figura 4. Schema a blocchi di un filtro di decimazione complesso

Figura 5. Illustrazione del filtraggio complesso (a) Segnale di ingresso tra 0 Hz ed FS/2 (b) Risposta del filtro passa-banda con decimazione per 8

Esempi pratici

Nelle applicazioni nel dominio del tempo, un filtro passa-basso digitale può rimuovere il rumore a frequenza più elevata sul segnale di ingresso. Nei casi in cui si campiona una forma d’onda a forma di impulso, il filtro passa-basso rimuove le armoniche di ordine superiore, rallentando quindi la frequenza del fronte dell’impulso.

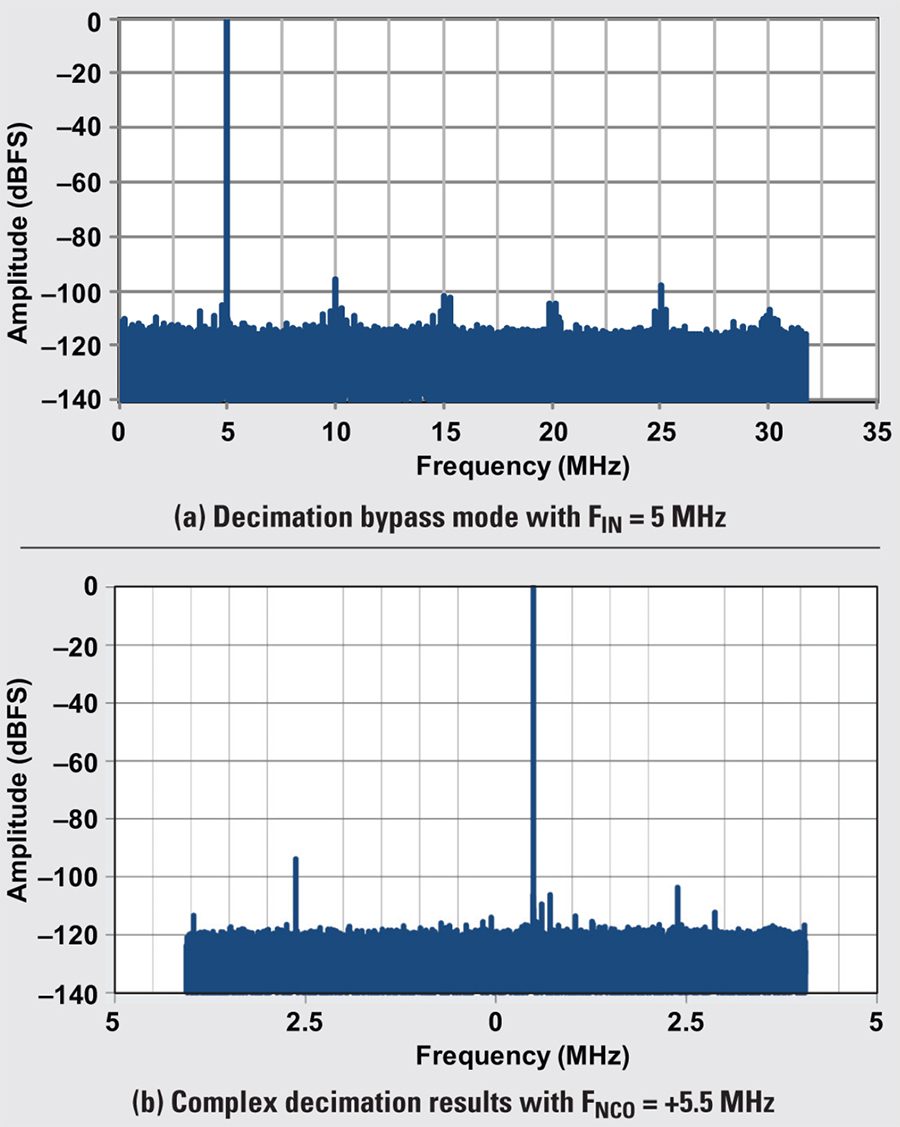

Nelle applicazioni nel dominio della frequenza, come i radar, il filtro di decimazione integrato risulta essere una funzionalità molto potente per i motivi descritti in precedenza in questo articolo. Come mostrato ulteriormente nella Figura 6, il segnale di ingresso FIN è campionato con FS = 65 MSPS, seguito da una decimazione complessa per 8 e una frequenza NCO di 5,5 MHz.

Figura 6. Esempio di prestazioni del filtro di decimazione integrato con FS = 65 MSPS

(a) Modalità di bypass della decimazione con FIN = 5 MHz

(b) Risultati complessi di decimazione con FNCO = +5,5 MHz

Conclusione

Nel tentativo di ridurre le dimensioni dei circuiti stampati e il costo della distinta base, i progettisti stanno cercando di sostituire i circuiti analogici con logica digitale/proprietà intellettuale (IP). I convertitori di dati SAR ad alta velocità con filtro digitale integrato, come quelli delle famiglie ADC35xx e ADC36xx, si adattano bene ad un’ampia gamma di applicazioni industriali. Analogamente ai convertitori delta-sigma, questi ADC semplificano i vincoli dei filtri analogici con un tasso di sovracampionamento più elevato, unito al filtraggio digitale integrato. Il mixer complesso, inoltre, può rimuovere uno stadio di miscelazione analogico, semplificando ulteriormente la catena del segnale front-end analogico.

Siti Web correlati

Informazioni sul prodotto:

[/boris]