Non ci sono prodotti a carrello.

Di Jeff Falin, Battery Charger Applications Engineer

Alvaro Aguilar, Member Group Technical Staff, Industrial Battery Charger Systems Manager

Introduzione

I moderni dispositivi elettronici portatili richiedono una batteria agli ioni di litio ad alta capacità per alimentare funzionalità diffuse come fotocamere ad alta definizione, touchscreen ad alta risoluzione edge-to-edge e connessioni dati ad alta velocità. Di conseguenza, sono aumentate le capacità di potenza in uscita delle fonti di alimentazione per la ricarica come l’USB Type-C® per consentire una ricarica più rapida di batterie ad alta capacità.

I tradizionali caricabatterie sincroni basati su buck non riescono a sfruttare completamente l’elevata potenza in ingresso a causa dei loro limiti in termini di massima efficienza. La sfida per i progettisti di dispositivi elettronici portatili sta nell’adattare una soluzione per la ricarica di batterie ad alta efficienza in un ingombro ridotto che sfrutti completamente l’elevata potenza in ingresso in modo da ottenere una ricarica rapida e senza surriscaldamenti.

Una topologia di convertitore a tre livelli che includa l’aggiunta di elementi capacitivi di immagazzinamento e di interruttori di alimentazione può aumentare la frequenza di commutazione equivalente, fSW, e generare una tensione inferiore attraverso l’induttore, che consente a sua volta il ricorso ad un induttore più piccolo. In questo modo, si migliora l’efficienza totale del sistema, con minori perdite di potenza e temperature di esercizio più basse in un ingombro ridotto rispetto ai tradizionali convertitori buck sincroni. Questo articolo presenta un’analisi della topologia buck a tre livelli e fornisce un confronto in termini di funzionamento e perdita di potenza tra i caricabatterie buck sincroni e i caricabatterie buck a tre livelli, comprese le variazioni nella corrente di carica tra le topologie buck a tre e due livelli.

Topologia buck tradizionale

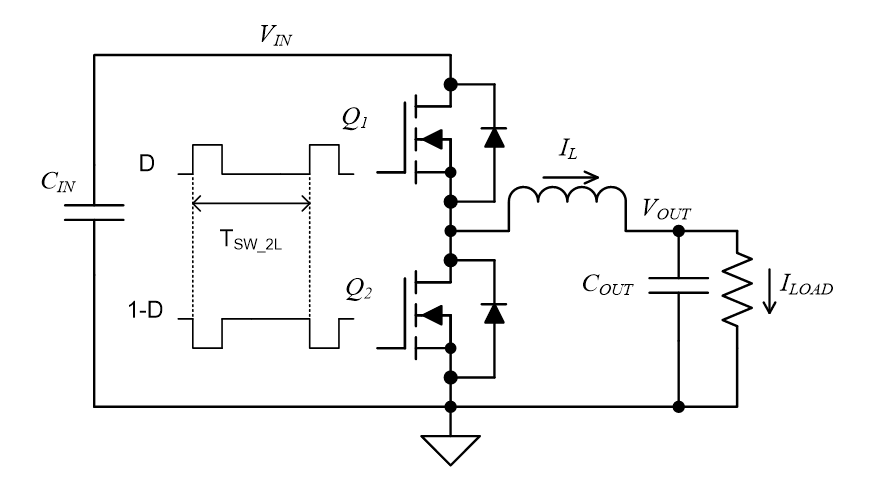

La topologia di commutazione sincrona a due livelli (2L), step-down (buck), esiste da decenni. Un convertitore buck tradizionale è costituito da due transistor a effetto di campo in silicio metaloossido (MOSFET o FET), un induttore, un condensatore di ingresso in parallelo alla sorgente di ingresso e un condensatore di uscita, come mostrato nella Figura 1.

I segnali di azionamento del gate degli interruttori sono complementari e funzionano con duty cycle D e 1 – D. Il nodo tra gli interruttori, VSW, si alterna tra VIN e 0 V; da qui viene il termine «convertitore a due livelli». Quando Q1 è acceso e Q2 è spento, l’induttore si sta caricando e fornisce corrente all’uscita. Quando Q2 è acceso e Q1 è spento, l’induttore si scarica e fornisce corrente all’uscita. Questo genera una forma d’onda quadrata con duty cycle fisso che, una volta filtrata dall’induttore e dal condensatore di uscita, fornisce una tensione di uscita.

Ipotizzando dei FET ideali e una corrente continua dell’induttore, il duty cycle a regime è D = VOUT/VIN. La fSW determina l’induttanza dell’induttore, basata su V = L × di/dt e riorganizzata come nell’Equazione 1:

![]()

dove K è l’ondulazione della corrente dell’induttore come percentuale della corrente di uscita, scelta tra il 20% e il 40%.

Per applicazioni di ricarica della batteria con ampi intervalli di tensione di ingresso, i processi esistenti per semiconduttori e la tecnologia degli induttori limitano fSW tra 1 e 2 MHz. Frequenze di commutazione più elevate provocano perdite di commutazione dei transistor e perdite in CA di secondo ordine dell’induttore per gestire le perdite del convertitore. Pertanto, quando si cerca di aumentare l’efficienza del convertitore e ridurre la dissipazione del calore, la soluzione più diffusa consiste nell’aumentare le dimensioni di ingombro dell’induttore per una resistenza CC inferiore (DCR).

Figura 1. Interruttori buck a due livelli (2L) e driver del gate

Funzionamento buck a tre livelli

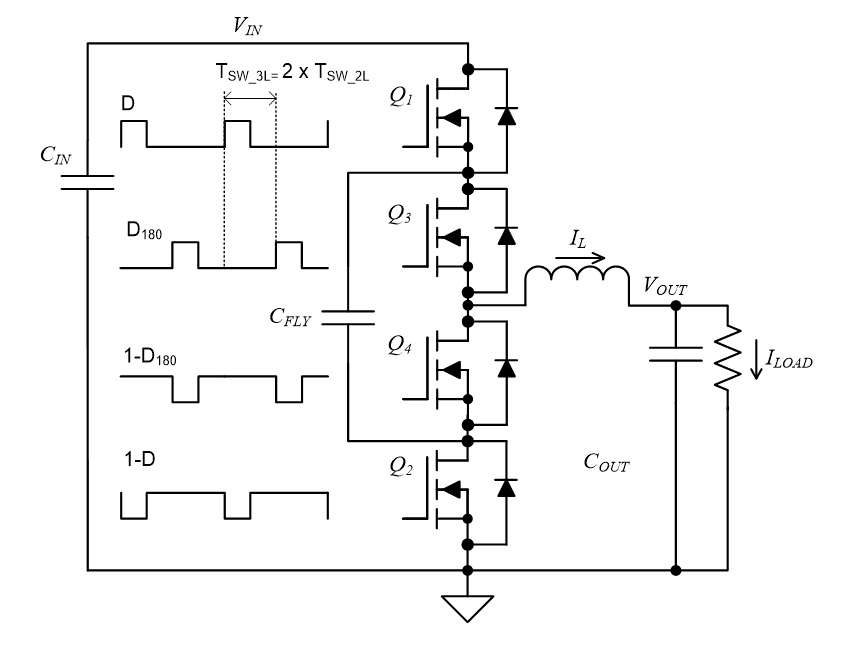

Il convertitore buck a tre livelli (3L) mostrato in Figura 2 è una combinazione tra un flying capacitor commutato, CFLY e un circuito induttore commutato, con due FET aggiuntivi, Q3 e Q4.

Lo schema di azionamento del gate è simile a quello di un convertitore buck bifase tradizionale. Un segnale complementare aziona i FET esterni, Q1 e Q2, con duty cycle D = VOUT/ VIN, proprio come il convertitore buck a due livelli (2L). Un secondo segnale complementare con lo stesso duty cycle aziona i FET interni, Q3 e Q4, ma è sfasato di 180 gradi rispetto al segnale del FET esterno. Mantenendo CFLY bilanciato a VIN/2, il nodo di commutazione VSW si alterna tra VIN, VIN/2 e terra; da qui viene il termine «tre livelli».

[boris]

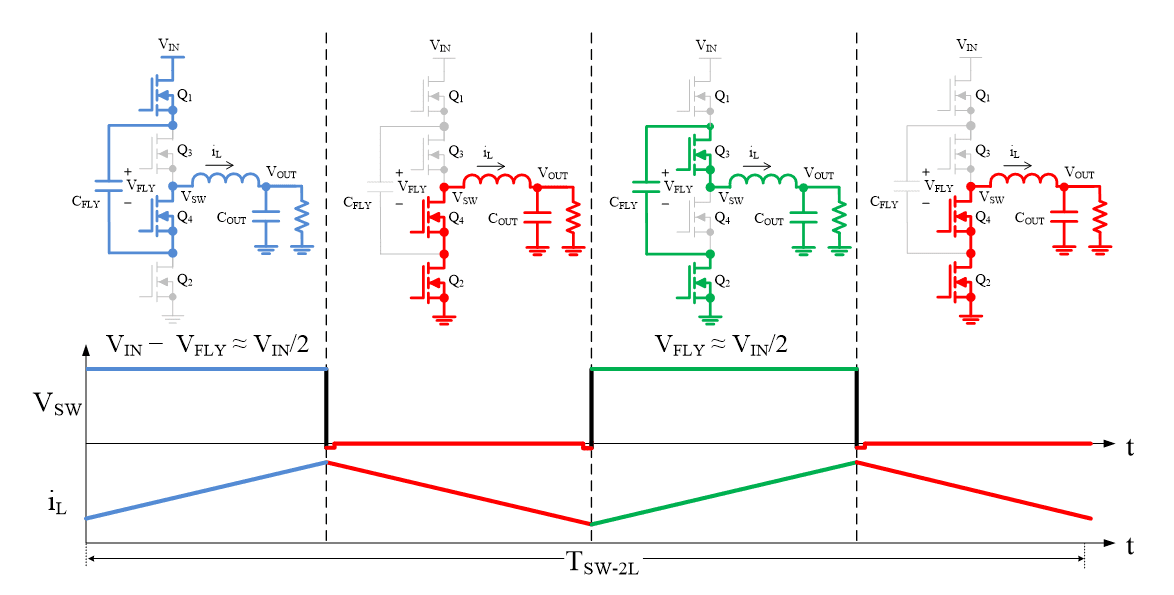

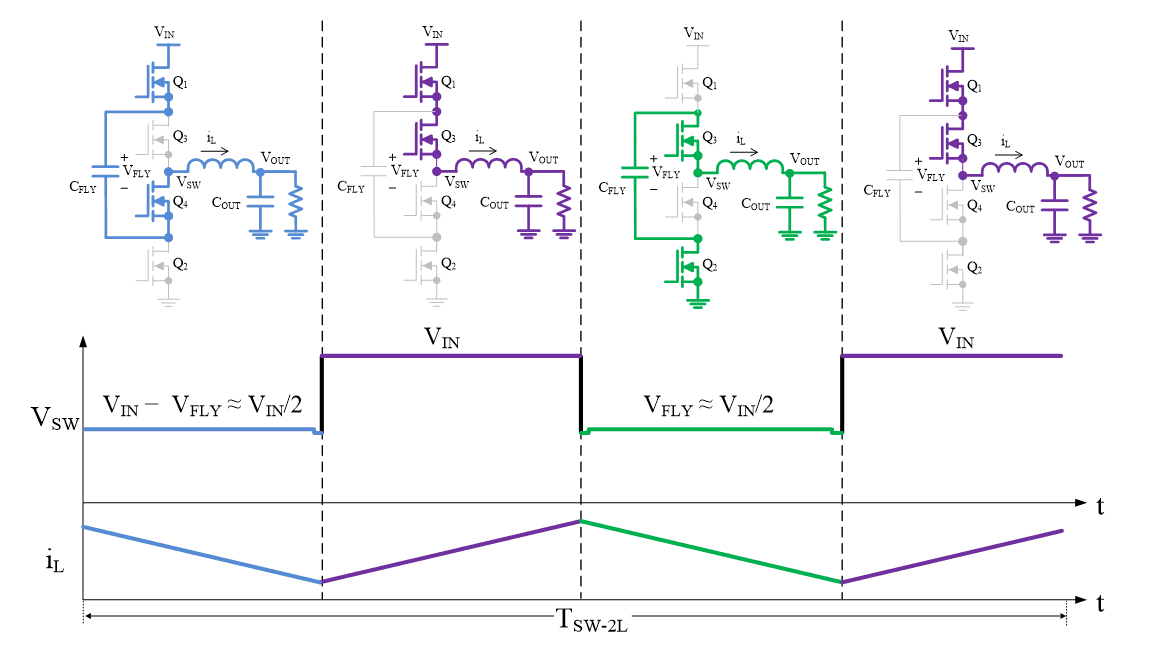

La Figura 3 mostra un ciclo di commutazione completo quando il duty cycle è inferiore a 0,5 (ovvero, quando la tensione di ingresso è più del doppio della tensione di uscita). La Figura 4 nella pagina successiva mostra il ciclo di commutazione completo quando il duty cycle è maggiore di 0,5.

Con D = 0,5 (50%), Q1 e Q4 sono attivi per metà del periodo; Q3 e Q2 sono attivi per l’altra metà. Di conseguenza, VSW rimane a VIN/2, che per definizione è uguale a VOUT. La tensione non attraversa l’induttore, quindi la corrente di ondulazione va a zero. Poiché i FET sono sfasati di 180°, la frequenza di commutazione, fSW_3L, sul nodo VSW è il doppio rispetto ad un convertitore 2L paragonabile, fSW_2L. Ogni FET si attiva solo una volta durante il periodo 2L, quindi TSW_2L = 2 × TSW_3L.

Figura 2. Interruttori buck a tre livelli (3L) e driver del gate

Figura 3. Funzionamento del convertitore a tre livelli (3L) con D minore di 0,5

Figura 4. Funzionamento del convertitore a tre livelli (3L) con D maggiore di 0,5

Perdite su chip buck a tre livelli (3L)

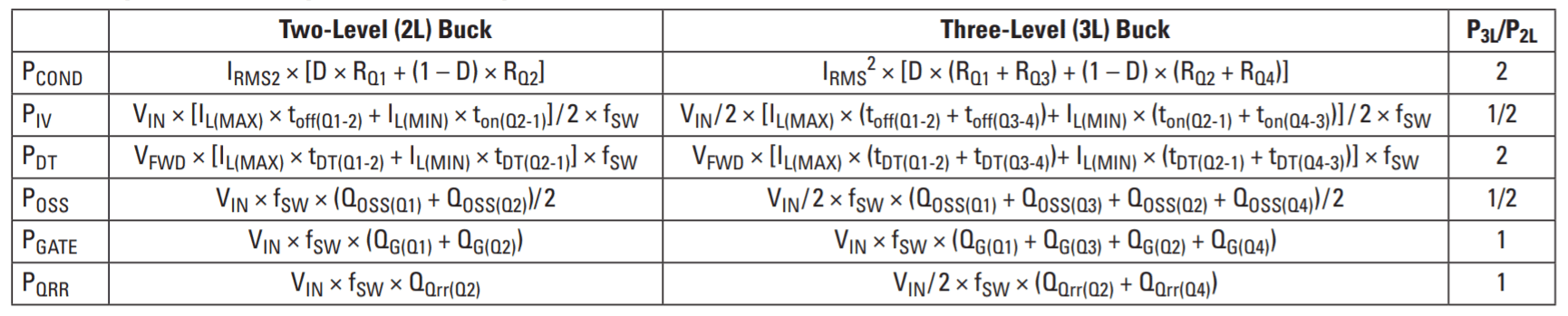

La Tabella 1 confronta le perdite su chip del convertitore buck 2L, PON-CHIP, con quelle nel convertitore buck 3L. Le perdite su chip comprendono le perdite di conduzione dalle resistenze degli interruttori, PCOND, le perdite di carica di commutazione, POSS e PGATE, le perdite per recupero inverso, PQRR, le perdite di corrente-tensione durante l’accensione e lo spegnimento del gate, PIV e la perdita attraverso i body diode durante il tempo morto quando entrambi gli interruttori sono spenti, PDT. Supponendo che CFLY sia bilanciato a VIN/2, i FET del convertitore buck 3L devono bloccare solo metà della tensione rispetto ai FET del convertitore buck 2L.

Fare le ipotesi precedenti sulle perdite per 2L e 3L consente di realizzare un confronto teorico delle perdite di potenza su chip tra le due topologie, come mostrato nella Tabella 1. I seguenti punti sono gli aspetti principali di questo confronto teorico:

- La fSW e l’ondulazione della corrente dell’induttore sono le stesse per entrambe le topologie, il che significa che il valore di induttanza per 3L, L3L, è un quarto di quella per 2L, L2L. Questo aspetto è spiegato più dettagliatamente nella sezione successiva.

- L’area occupata dal FET high-side (HS) 2L è uguale alla somma dell’area per il FET HS 3L (ossia, AQ1-2L = AQ1-3L + AQ3-3L). Con i FET 3L a metà della tensione nominale del FET 2L, le resistenze FET sono uguali (ossia, RQ1-2L = RQ1-3L = RQ3-3L). Lo stesso vale per i FET low-side. Questo si traduce in una resistenza FET totale per 3L che è il doppio rispetto a quella per 2L per un’area fissa.

- Se i FET 3L sono a metà della tensione del FET 2L ma i FET 3L sono pilotati con le stesse tensioni transitorie, dv/dt, a VSW, i tempi di accensione e spegnimento vengono dimezzati. Ne deriva che PIV è ridotta della metà.

- Utilizzando la stessa area, la carica totale immagazzinata rimane la stessa: in pratica, significa che QOSS(Q1)-2L = QOSS(Q1)-3L + QOSS(Q3)-3L ed è lo stesso per QOSS(Q2)-2L. La carica totale immagazzinata è in realtà inferiore perché i FET 3L sono a metà della tensione, ma questo punto può essere ignorato in un’analisi semplice.

Tabella 1. Equazioni per confronto della perdita di potenza stimata

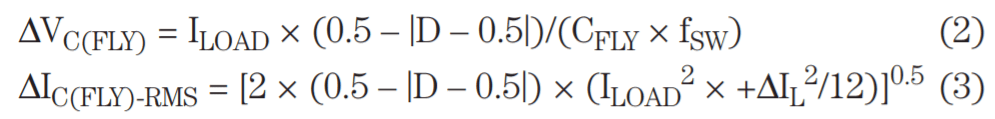

Come mostrato nella colonna più a destra della Tabella 1, per la stessa area del die, la conduzione della topologia 3L e le perdite dell’intervallo di attesa raddoppiano. Ma poiché i FET 3L hanno la metà della tensione di ingresso rispetto al buck 2L, le perdite POSS e PIV sono dimezzate. Un aumento dell’area del FET consente di ridurre le perdite di conduzione fino a quando le perdite di commutazione iniziano ad essere predominanti, come mostrato nella Figura 5.

Le aree FET ottimali, AOPT-2L e AOPT-3L, si hanno quando le perdite di commutazione sono uguali alle perdite di conduzione.

Componenti fuori chip buck a tre livelli (3L) e relative perdite

Le perdite fuori chip includono quelle attraverso la resistenza in serie equivalente (ESR, equivalent series resistance) nei condensatori di ingresso, uscita e nei flying capacitor, nonché nell’induttore. La scelta di condensatori ceramici con ESR bassissima (<20 mΩ) rende le loro perdite quasi trascurabili. Anche i condensatori di ingresso e di uscita per il convertitore 3L sono dimensionati in base alla corrente di ondulazione di ingresso e all’ondulazione della tensione di uscita accettabili, proprio come per un convertitore 2L.

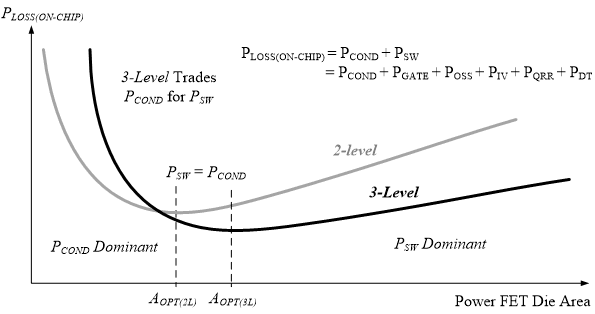

Il dimensionamento di CFLY per una tensione e una corrente di ondulazione accettabili è fondamentale per il funzionamento del 3L. Infatti, mantenere CFLY bilanciato a VIN/2 durante i transitori, l’avvio, a carico leggero e D = 100% non è banale e richiede alcuni circuiti proprietari aggiuntivi non mostrati nella Figura 2. La Figura 6 mostra un esempio di forma d’onda per ΔIFLY a ΔIL normalizzato.

Le Equazioni 2 e 3 sono per tensione e corrente di ondulazione di CFLY:

La tensione di ondulazione di CFLY raggiunge il picco a D = 0,5 e aumenta direttamente con la corrente di carico. Dopo aver preso in considerazione il derating del condensatore ceramico dalla polarizzazione CC e dalla temperatura, CFLY deve resistere alla metà della tensione di ingresso. Si ricorda che con D = 0,5 la corrente di carico di IC (FLY) è massima. La capacità di CFLY è dimensionata per mantenere ΔVC(FLY) a meno del 10% di VIN/2 per garantire la stabilità del loop. Per garantire una lunga durata del condensatore, la dimensione del package del condensatore e la corrente nominale RMS devono essere di dimensioni sufficienti a gestire l’aumento di temperatura correlato.

Le perdite dell’induttore sono costituite da perdite DCR, PDCR, e perdite del core, PCORE. Le perdite DCR aumentano con il valore di induttanza, che è una funzione di fSW.

Figura 5. Perdite su chip rispetto all’area del die

Figura 6. Tensione e corrente di ondulazione di CFLY rispetto alla corrente di ondulazione dell’induttore

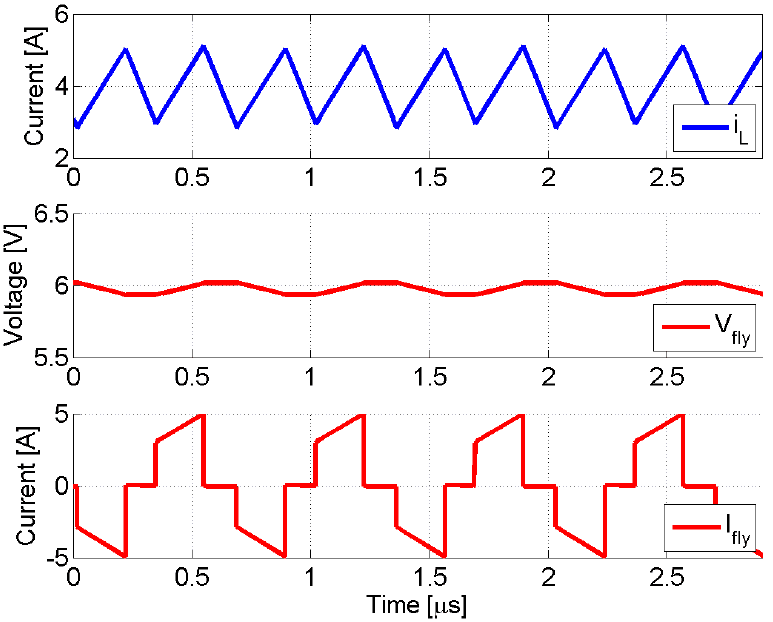

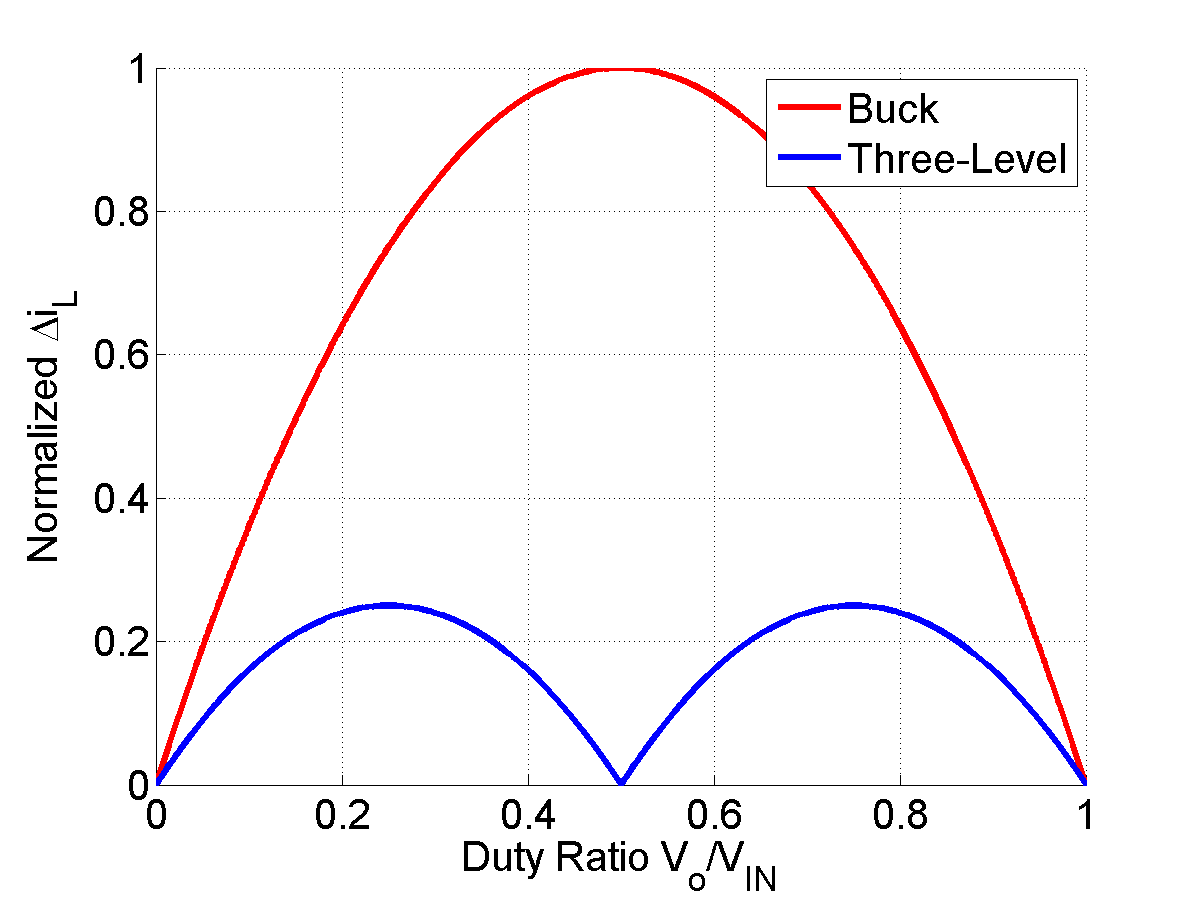

Il driver del gate con spostamento di fase di 180 gradi per Q3 e Q4 raddoppia efficacemente la frequenza di commutazione del convertitore a VSW. Inoltre, tenendo CFLY bilanciato a VIN/2, il convertitore a tre livelli riduce della metà i volt per secondo sull’induttore. La combinazione si traduce in una riduzione di un quarto dell’ondulazione dell’induttore, dati lo stesso induttore e fSW. La riduzione della corrente di ondulazione dell’induttore rispetto alla commutazione del convertitore 2L alla stessa frequenza durante il duty cycle è evidente nella Figura 7.

Figura 7. Confronto del duty cycle dei convertitori 2L e 3L

In un convertitore 3L, dall’Equazione 4 deriva il valore di induttanza:

![]()

e l’Equazione 5 calcola le perdite DCR dell’induttore:

![]()

L’Equazione 5 conferma che l’ondulazione della corrente dell’induttore ha uno scarso effetto su PDCR. Come il convertitore buck 2L, il convertitore 3L richiede un induttore con DCR inferiore per una maggiore efficienza. Come spiegato in precedenza, la topologia fornisce intrinsecamente una riduzione di un quarto della corrente di ondulazione dell’induttore. Se l’applicazione è in grado di accettare la corrente di ondulazione dell’induttore e l’ondulazione della tensione di uscita risultanti da un convertitore 2L paragonabile che opera alla stessa frequenza di commutazione, è possibile utilizzare un induttore con un quarto del valore di induttanza, che è disponibile in un package con un ingombro minore.

Ipotizzando che l’induttore DCR scali proporzionalmente al valore di induttanza, le perdite dell’induttore per il convertitore 3L, PDCR-3L, sono un quarto di quelle del convertitore 2L, PDCR-2L/4. Il package più piccolo porta a ridurre le dimensioni totali della soluzione, mentre il la DCR inferiore produce una maggiore efficienza. Pertanto, a parità di budget termico, questi vantaggi consentono al convertitore 3L di fornire una corrente di uscita maggiore in un’area più piccola (ovvero una densità di potenza maggiore) rispetto ad una soluzione buck 2L.

Confronto tra soluzioni di ricarica buck 3L e 2L

Il più recente caricatore buck 3L a cella singola di TI, il BQ25910, opera a fSW = 750 kHz ed è in grado di fornire 5 A di corrente per la ricarica di batterie. Per confronto, il caricabatterie BQ25898 4-A 2L di TI viene fornito in un package simile a livello di chip, con una tecnologia di processo al silicio più vecchia, ma opera a fSW = 1,5 MHz. Il BQ25898 utilizza un induttore da 1 μH mentre il BQ25910 utilizza un induttore da 470 nH, pari solo alla metà e non potenzialmente ad un quarto dell’induttanza consentita dalla topologia 3L.

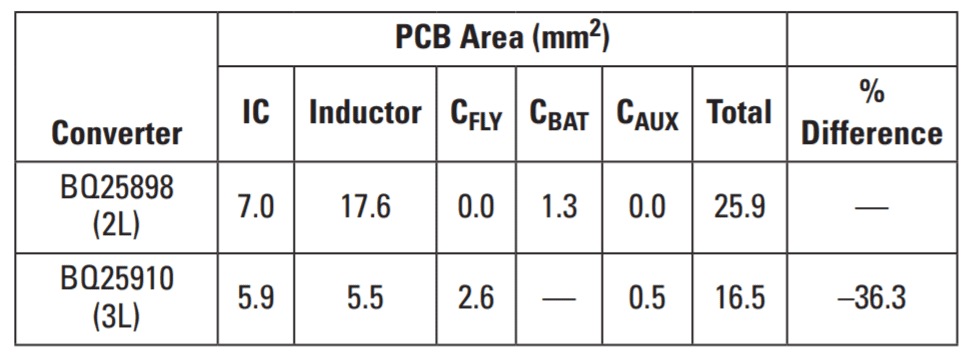

La Tabella 2 confronta le aree dei componenti per i due caricabatterie, utilizzando induttori con valori nominali di corrente simili e DCR ragionevole. La tabella esclude anche il routing e ignora i componenti comuni per entrambi i caricabatterie, come il condensatore di ingresso, il condensatore a pin PMID e il condensatore del regolatore lineare.

Tabella 2. Confronto delle aree dei componenti

Anche con i condensatori aggiuntivi, l’ingombro ridotto del BQ25910, ma con induttore DCR simile, e la mancanza di FET della batteria si traducono in una riduzione del 36% dell’area del circuito stampato (PCB).

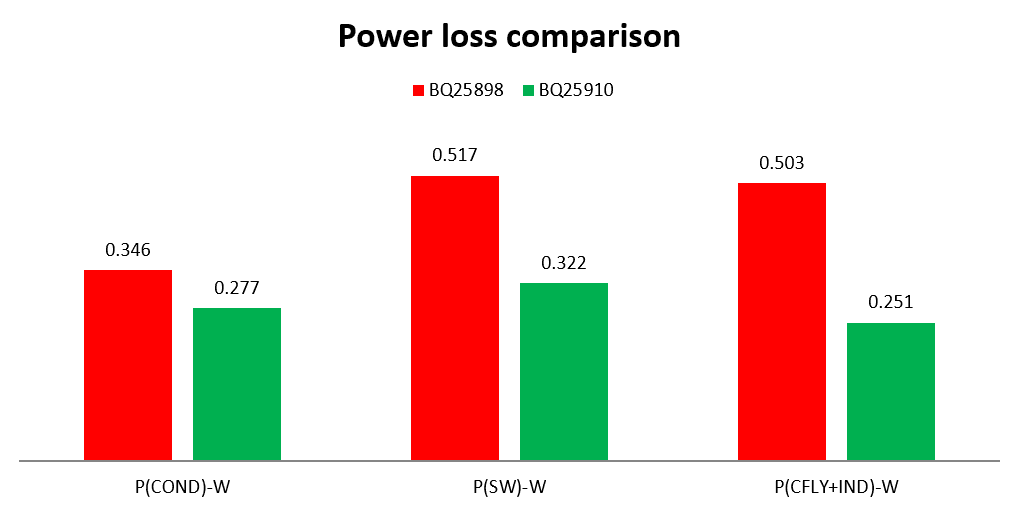

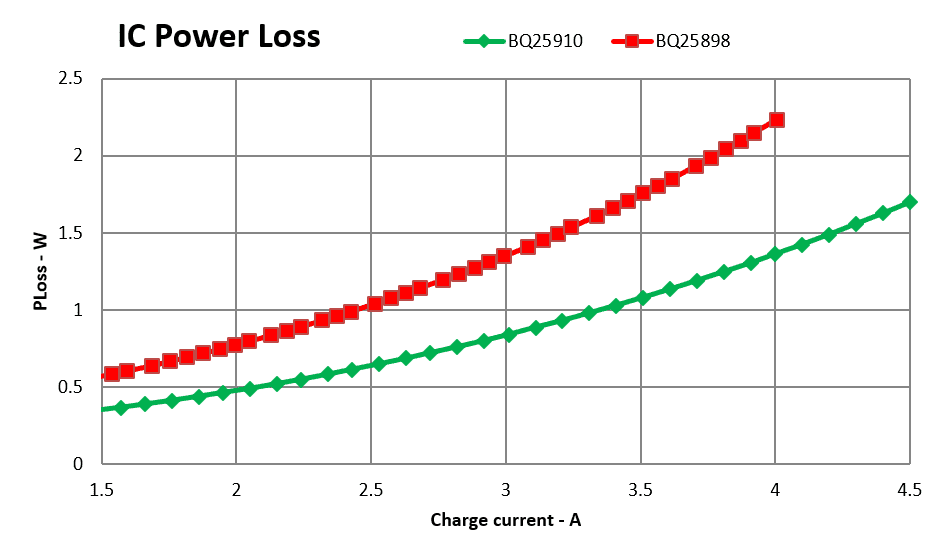

La Figura 8 mostra le perdite di potenza per il BQ25910, modellate utilizzando le equazioni nella Tabella 1 e i dati dell’effettivo processo al silicio. Sono mostrate anche le perdite per il BQ25898. Si noti come le perdite DCR dell’induttore sono dominanti sulle perdite totali per entrambi i caricabatterie.

Figura 8. Confronto fra le perdite di potenza di BQ25910 e BQ25898

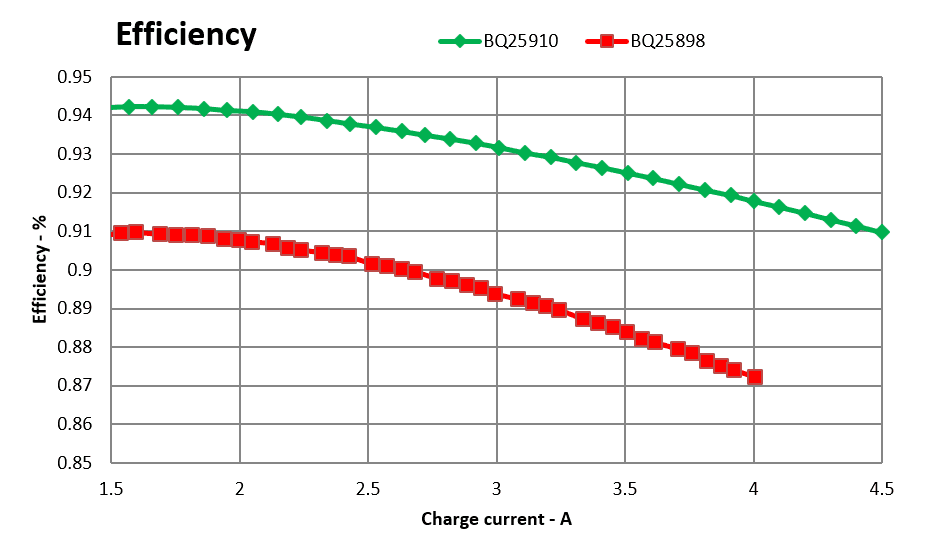

La Figura 9a mostra un grafico dell’efficienza misurata di BQ25910 e BQ25898 con una tensione di ingresso di 9 V e una tensione della batteria di 3,8 V. La Figura 9b confronta le perdite dei due convertitori. Con una corrente di carica di 3 A, l’efficienza del BQ25898 è dell’89,3%. Nella Figura 8, la PLOSS del BQ25910 è 0,850 W da una potenza di uscita totale di 3 A × 3,8 V = 11,4 W, con un’efficienza del 93,1%, che è molto vicina al 93,2% misurato.

Con una tensione di ingresso di 9 V, una tensione della batteria di 3,8 V e una corrente di carica di 3 A, il BQ25910 3L presenta un miglioramento dell’efficienza del 3,9% e una riduzione delle perdite del 36%. Per un budget di perdita di 1,5 W, il BQ25898 può erogare 3,2 A di corrente di carica, mentre il BQ25910 può erogare 4,2 A di corrente di carica (un aumento del 31%) in una soluzione di dimensioni inferiori del 36%.

Figura 9a. Misurazione dell’efficienza di BQ25910 e BQ25898

Figura 9b. Misurazione delle perdite di potenza di BQ25910 e BQ25898

Conclusione

I consumatori richiedono dispositivi elettronici personali con batterie di capacità sempre crescenti e vogliono che si ricarichino il più rapidamente possibile. Raggiungere un’efficienza superiore al 90% per correnti di carica da 3 A e superiori da un alimentatore da 9 V o più in un ingombro ridotto rimane difficile con i tradizionali caricabatterie a commutazione buck 2L. Sono necessarie soluzioni di ricarica della batteria che si adattino ad un ingombro minimo fornendo la corrente di carica ottimale, non solo per una maggiore sicurezza e durata della batteria, ma anche per avere tempi di ricarica e temperatura del dispositivo accettabili. I caricabatterie a commutazione buck 3L offrono una maggiore efficienza riducendo le dimensioni totali della soluzione per soddisfare requisiti di design compatto.

Siti Web correlati

Video del caricabatterie buck a tre livelli (scorrere verso il basso per il video)

[/boris]