Non ci sono prodotti a carrello.

di Philip Pratt, Product Marketing Engineer, High-speed Data Converters, Texas Instruments

I progettisti di hardware che utilizzano convertitori di dati ad alta velocità si trovano ad affrontare notevoli sfide relative a input, output, frequenze di clock e interfaccia digitale ad alta frequenza nella progettazione, ad esempio, di sistemi aerospaziali e di difesa, apparecchiature di test e misurazione o front end analogici per LiDAR nell’automotive (AFE). Le problematiche possono riguardare il collegamento con un FPGA (field-programmable gate array) nella speranza che la prima versione del progetto funzioni o per determinare il modo migliore per modellare il sistema prima di costruirlo.

Rapido sviluppo del sistema

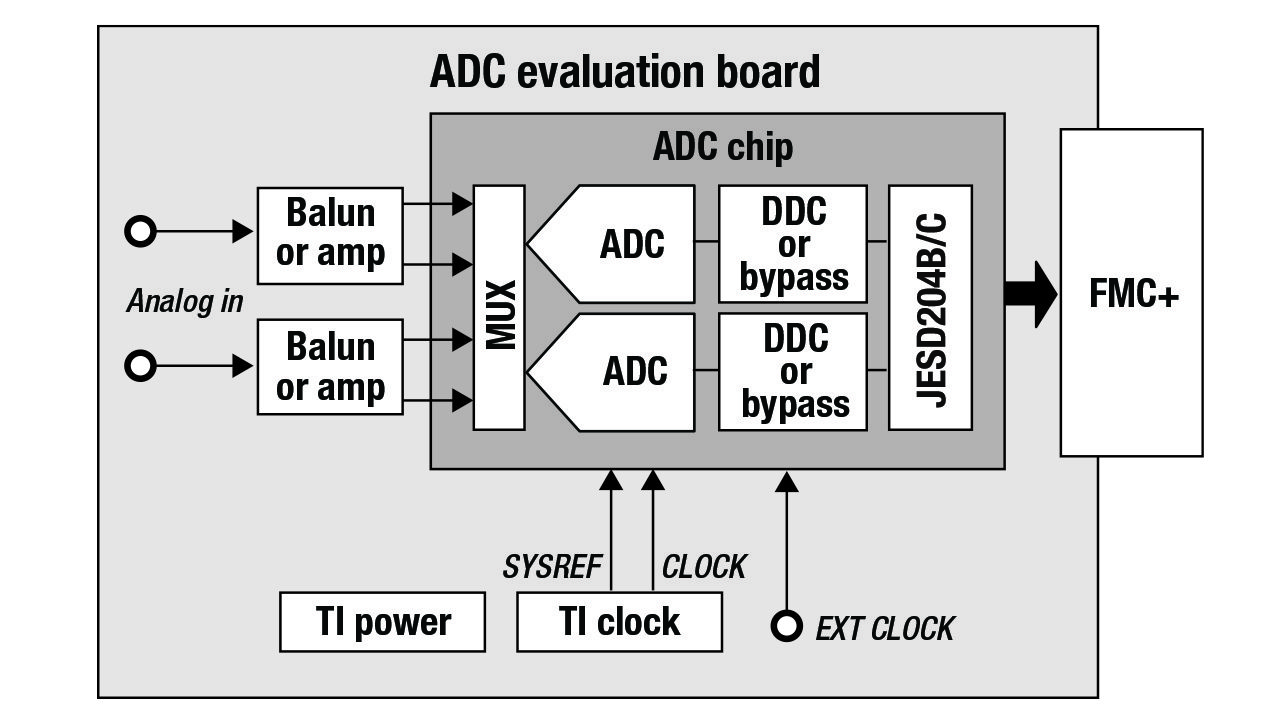

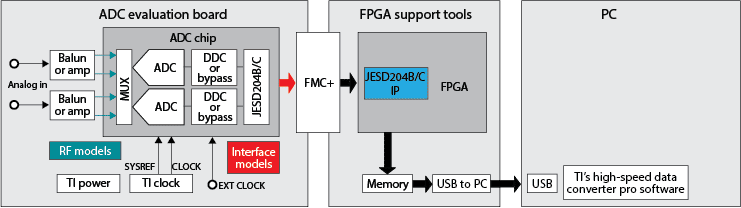

Prima di avviare un nuovo progetto hardware, gli ingegneri valutano spesso i chip più importanti sul banco di prova. Una volta trovate le apparecchiature necessarie per far girare una tipica scheda di valutazione, la valutazione dei componenti avviene solitamente con forniture e fonti di segnale notevolmente idealistiche. Il compito di TI in molti casi consiste nel fornire alimentazione e clock su scheda in modo da poter iniziare a far girare la scheda con il minimo in termini di apparecchiature sul banco di prova e con alimentazioni e fonti di segnale più realistiche, come ad esempio nella configurazione mostrata in Figura 1.

Figura 1: Scheda di valutazione ADC tipica

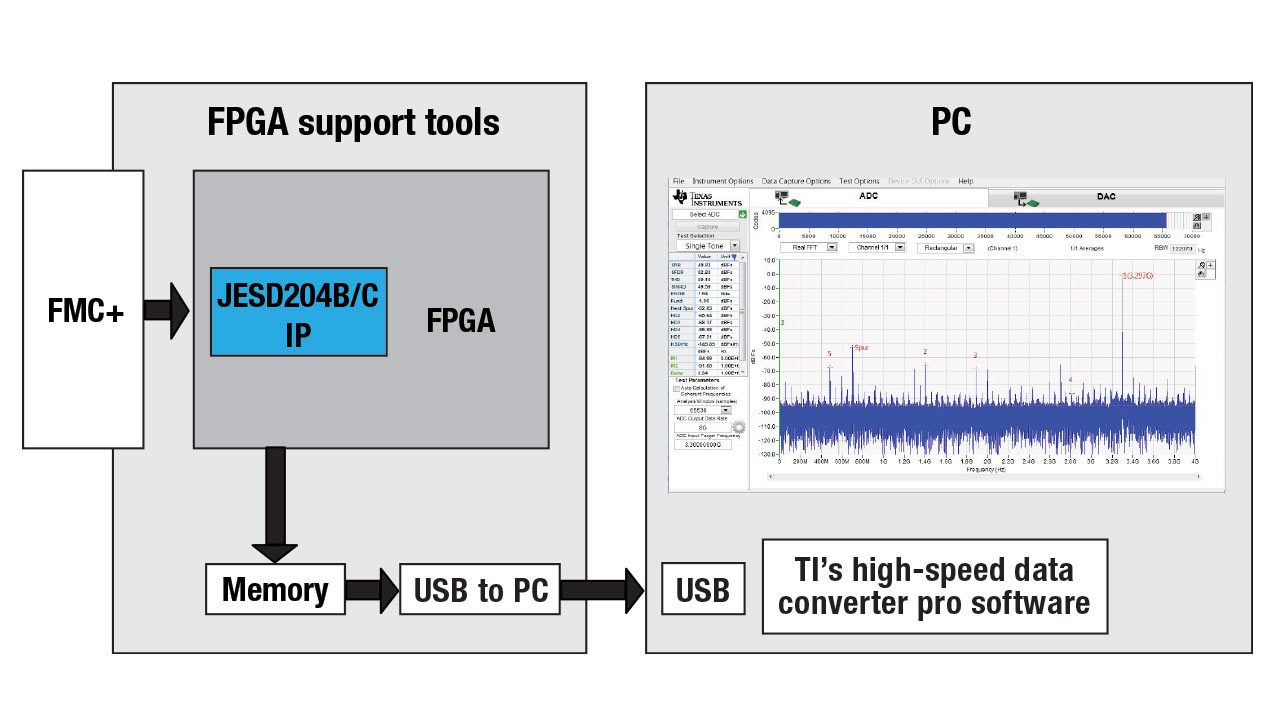

Una volta validate le prestazioni, è possibile utilizzare gli schemi e il layout di una scheda di valutazione più completa come progetto di riferimento per la porzione di sottosistema interessata. I nostri strumenti di acquisizione dei dati e di generazione dei pattern supportano CMOS, LVDS e JESD204 e sono forniti con il software necessario per il loro funzionamento. Utilizzando il manuale utente della scheda di valutazione per un convertitore di dati ad alta velocità è possibile mettere in funzione la maggior parte delle schede in meno di 10 minuti. Vedere la Figura 2.

Figura 2: Hardware e software per acquisizione dei dati e generazione dei pattern di TI

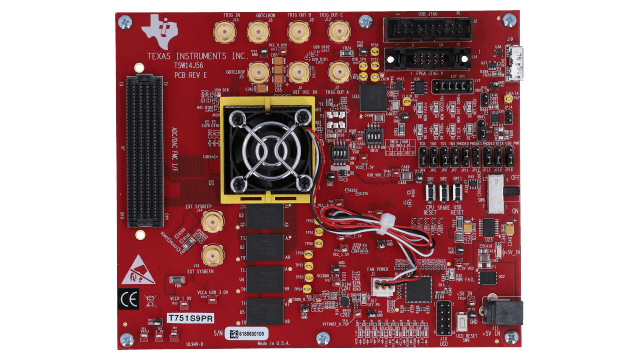

Poiché i sistemi diventano sempre più complicati, potrebbe essere necessario valutare un’ampia gamma di casi d’uso. A tal fine può essere utile una scheda di valutazione. Se le esigenze di valutazione si fanno complesse, è possibile utilizzare software Python, Matlab, Labview o C++ per comunicare direttamente attraverso la scheda di valutazione del dispositivo, la soluzione per la scheda di acquisizione e le apparecchiature sul banco di prova. Validi esempi di schede di supporto sono la TSW1400EVM per LVDS/CMOS oppure la TSW14J56EVM per il supporto dei dispositivi con protocollo serializzatore-deserializzatore JESD204B (SerDes), come mostrato in Figura 3.

Figura 3: TSW14J56EVM di TI per l’acquisizione dei dati o la generazione dei pattern JESD204B

Inoltre, TI supporta anche un mockup completo a livello di sistema di un prototipo di modulo per valutazione multipla da un singolo PC. Ad esempio, è possibile testare simultaneamente i canali di trasmissione e ricezione collegando un kit di sviluppo FPGA Xilinx come KCU105 o VCU118 a più convertitori analogico/digitale (ADC) o convertitori digitale/analogico (DAC).

Connettività FPGA e JESD204B e JESD204C

Uno dei principali problemi da risolvere potrebbe essere la trasmissione di dati da e verso l’FPGA. Benché LVDS e CMOS siano interfacce semplici, sono molto limitate in termini di velocità che possono supportare per ciascun pin sul dispositivo. Poiché i più recenti convertitori di dati ad alta velocità supportano più comunemente frequenze di input o output >1 GSPS, queste interfacce si trovano col fiato corto oppure si dimostrano non così semplici da usare per la progettazione.

JEDEC, che sviluppa standard aperti per l’industria della microelettronica, ha creato JESD204 per risolvere questo problema supportando frequenze per lane a coppia differenziale superiori a 12,5 Gbps. Tuttavia, mentre JESD204 permette di ridurre il numero dipinto, comporta anche un aumento della complessità dell’interfaccia a causa della codifica e della serializzazione, o per via della deserializzazione e della decodifica, dei dati paralleli.

Finora, è stato fondamentalmente necessario affidarsi a blocchi di proprietà intellettuale (IP) JESD204 e al supporto coperto dai fornitori di FPGA. Nonostante questi blocchi IP funzionino molto bene, sono forniti in modo da supportare qualsiasi dispositivo in qualsiasi configurazione: ciò significa che può essere difficile programmarli e configurarli per il proprio specifico caso d’uso. È quindi necessario dedicare un notevole impegno alla progettazione dell’IP in prima persona oppure cercare un’IP da un fornitore di IP terzo. Tuttavia, l’IP di terze parti richiede aiuto e supporto per l’implementazione se qualcosa va storto.

La nostra JESD204 Rapid Design IP è preconfigurabile e utilizzabile in modo specifico per la vostra piattaforma FPGA, per il convertitore di dati e per la modalità JESD204. La nostra IP richiede meno risorse FPGA, oltre ad essere personalizzata per ciascun uso particolare. Un altro vantaggio sta nel fatto che sono necessarie soltanto ore o giorni per implementare un collegamento JESD204, anziché settimane o mesi.

Modelli di dispositivo

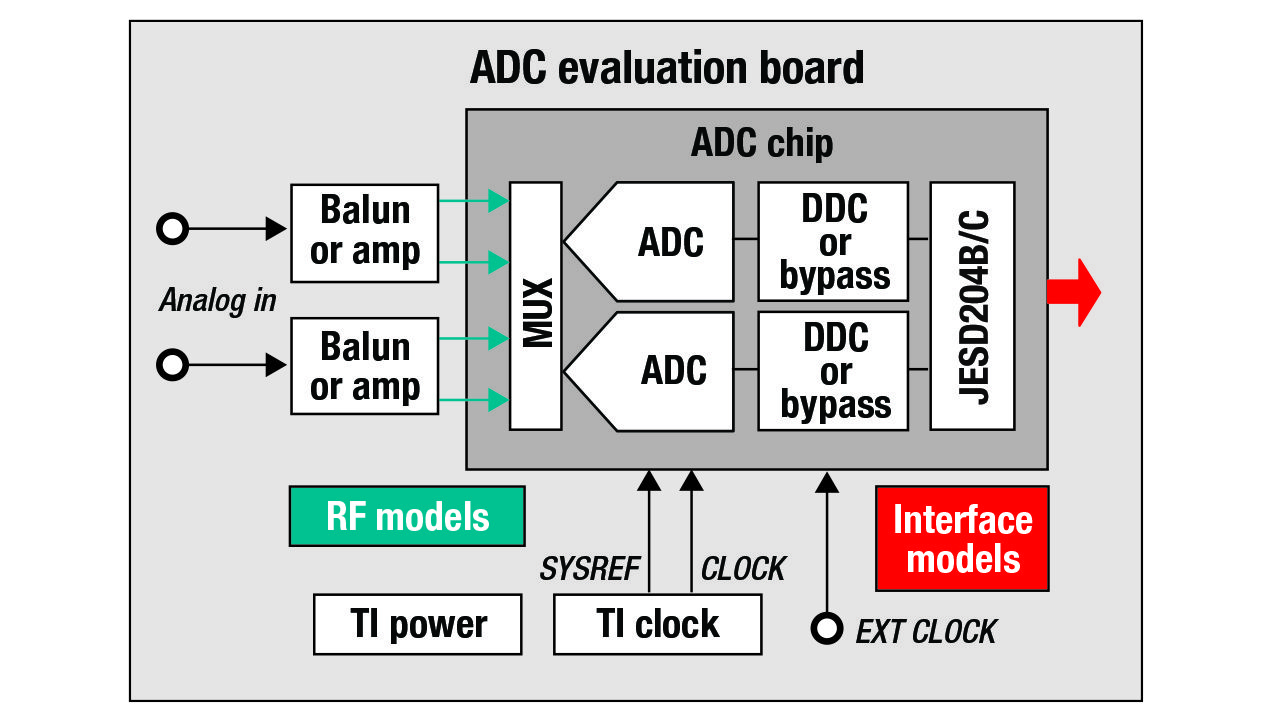

Poiché il campionamento diretto a radiofrequenza (RF) e i SerDes estremamente veloci stanno diventando sempre più diffusi in combinazione con convertitori di dati ad alta velocità, la possibilità di modellare l’integrità in RF e di segnale sta divenendo una necessità per portare a termine un progetto al primo colpo. Tradizionalmente, la maggior parte dei fornitori fornisce solo informazioni sull’impedenza in ingresso per ADC in modelli con parametri S, ma i nostri dispositivi di input ad alta frequenza ADC12DJ3200, ADC12DJ5200RF e ADC12QJ1600-Q1, destinati a frequenze di campionamento fino a 8 GHz, offrono ora modelli con parametri S che includono informazioni su impedenza e risposta in frequenza.

Con questo nuovo modello è possibile simulare il comportamento previsto del dispositivo e ottimizzare l’adattamento di impedenza. La strategia di TI consiste nell’offrire questi modelli su dispositivi che supportano frequenze di ingresso e uscita molto elevate, dove l’adattamento di impedenza e il raggiungimento della risposta in frequenza desiderata risultano più impegnativi.

Sul lato dell’interfaccia digitale del convertitore di dati, l’IBIS (Input/Output Buffer Information Specification) costituisce un modello prevalente che fornisce informazioni sullo strato fisico per i pin di CMOS e LVDS, nonché comportamenti per tipi in CC e CA. Poiché la maggior parte dei nuovi convertitori di dati utilizza SerDes JESD204 ad alta velocità, i modelli hanno visto un miglioramento verso l’IBIS-AMI (Algorithmic Modeling Interface), che comprende informazioni utili per l’applicazione dell’equalizzazione e per la pre- e post-enfasi. IBIS-AMI offre la modellazione necessaria per ottenere il risultato giusto dalla vostra scheda al primo colpo, raggiungendo al tempo stesso buoni risultati in termini di rapporto bit/errore, integrità del segnale e un affidabile collegamento dati. La Figura 4 mostra modelli RF (verde) e con interfaccia digitale (blu).

Figura 4: Modellazione dell’interfaccia

Conclusione

Se è passato parecchio tempo dall’ultima volta che avete progettato con convertitori di dati ad alta velocità o se il mondo della progettazione ad alta velocità vi è relativamente nuovo, sarete lieti di sapere che TI sta rendendo il tutto più semplice da usare. Abbiamo messo insieme un ambiente di sviluppo completo per semplificare il tutto, come mostrato in Figura 5.

Grazie all’IP pronta all’uso per una facile integrazione FPGA, ai modelli di sistema RF precisi ed alla più affidabile gamma di moduli di valutazione flessibili, scalabili e automatizzabili sul mercato, è possibile ridurre di mesi il tempo di sviluppo del firmware, ridurre i costosi cicli di progettazione e velocizzare la progettazione ad alta velocità dalla concezione al prototipo.

Figura 5: Tipico ambiente di valutazione per convertitore analogico/digitale (ADC) ad alta velocità