Non ci sono prodotti a carrello.

di Pablo Trujillo

I filtri digitali eseguiti su hardware embedded o FPGA utilizzano quasi sempre l’aritmetica a virgola fissa. Gli effetti della quantizzazione devono essere verificati durante lo sviluppo, preferibilmente tramite hardware in-the-loop. Utilizzando MATLAB e una scheda FPGA Eclypse Z7 con Zmod per la conversione dei dati, è facile.

Quando sentiamo la frase “software per l’ingegneria”, la maggior parte di noi ingegneri pensa immediatamente a MATLAB. Ci sono poche aree dell’ingegneria per le quali MATLAB non fornisce un pacchetto e il digital signal processing e il design di FPGA non sono sicuramente tra queste.

La Signal Processing Toolbox di MATLAB offre agli sviluppatori tutte le funzionalità di cui hanno bisogno per creare un filtro o qualsiasi sistema di elaborazione del segnale. Il Fixed-Point Designer consente loro di quantizzare i propri dati e li aiuta a implementare algoritmi a virgola fissa e a virgola mobile nel loro sistema di elaborazione e a verificarne gli effetti sul sistema digitale. E pacchetti come HDL Coder, HDL Verifier e FPGA Data Capture consentono loro di testare il loro progetto su un vero FPGA come hardware in-the-loop e di trasferire il sistema risultante sulla loro scheda FPGA. In questo modo, la creazione di un sistema di elaborazione del segnale diventa meno complessa.

Figura 1: La scheda FPGA Eclypse Z7 Zynq-7000 viene utilizzata come hardware in-the-loop

Supponiamo di voler progettare un filtro passa-banda per un sistema di comunicazione per estrarre un certo segnale da una linea che utilizza il multiplexing a divisione di frequenza. Questa tecnica è utilizzata da tempo, ad esempio, per trasmettere diverse stazioni radio sulla stessa linea dati: l’aria.

Un altro caso è la Power Line Communication (PLC), dove possiamo trasferire energia a frequenze di rete di 50Hz o 60Hz e dati a frequenze di diverse centinaia di kilohertz. E una volta che il filtro è stato progettato, vogliamo eseguirlo su un hardware reale.

Questo sistema hardware potrebbe comprendere, ad esempio, una scheda FPGA SoC (System on Chip) Eclypse Z7 Zynq-7000 di Digilent con un modulo oscilloscopio Zmod Scope 1410 a 2 canali a 14 bit e un modulo generatore di forme d’onda arbitrarie Zmod AWG 1411 a 2 canali a 14 bit, entrambi prodotti da Digilent, montati sulla parte superiore.

Con l’aiuto del convertitore analogico-digitale (ADC) dello Zmod Scope 1410 possiamo digitalizzare il segnale di linea ed emettere sia il segnale campionato che quello filtrato, attraverso il convertitore digitale-analogico (DAC) sul Zmod AWG, mentre eseguiamo il filtro stesso sullo Zynq-7000.

Progettazione del filtro e cura della quantizzazione

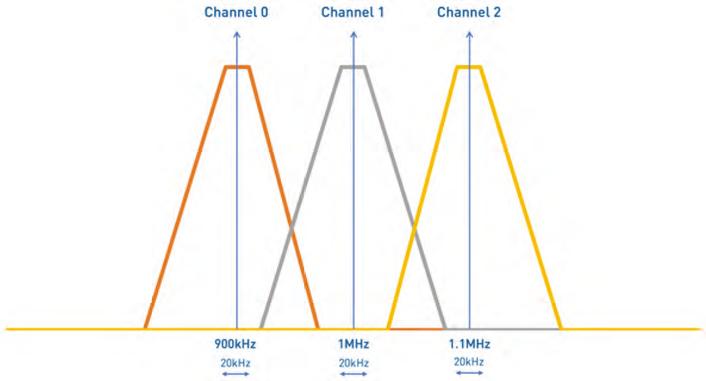

La Figura 2 mostra lo spettro di frequenza della nostra linea di trasmissione. Ogni canale ha una larghezza di banda di 20 kHz, e i canali sono distanziati di 100 kHz. Il nostro canale di interesse è il canale 1, e progetteremo il nostro filtro passa-banda per evitare interferenze dagli altri canali.

Per fare questo, dobbiamo garantire un’attenuazione di almeno -60 dB alla larghezza di banda degli altri canali. Per ottenere questa caratteristica, il nostro filtro dovrebbe avere una banda passante compresa tra 990kHz e 1010kHz, una banda di arresto a frequenza inferiore compresa tra 0Hz e 910kHz e una banda di arresto a frequenza più alta a partire da 1090kHz.

Figura 2: Lo spettro di frequenza della linea di trasmissione di esempio.

Il segnale di interesse è il canale 1.

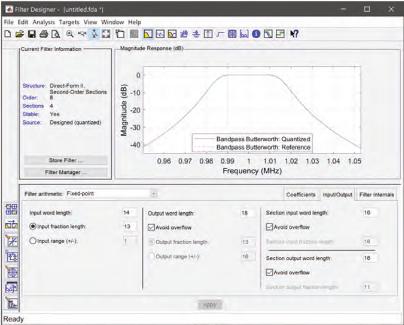

Con l’aiuto dello strumento Filter Designer di MATLAB possiamo configurare tutti questi aspetti del nostro filtro digitale. Per il nostro esempio, utilizziamo un filtro Butterworth IIR (Infinite Impulse Response), perché ci consente di progettare un filtro di ordine basso con un’elevata attenuazione e perché ha una banda passante abbastanza piatta.

La frequenza di campionamento sarà scelta per soddisfare sia i requisiti hardware dei nostri convertitori di dati (105MSPS per l’ADC AD9648-105 di Analog Devices sullo Zmod Scope e 100MSPS per il DAC AD9717, sempre di Analog Devices), sia il teorema di campionamento di Nyquist. Per il nostro esempio, sono sufficienti 10 MSPS.

Inoltre, poiché i nostri convertitori di dati sono dispositivi a virgola fissa a 14 bit, dobbiamo quantizzare i dati del filtro tramite il pannello Filter Quantization del Filter Designer Tool in modo che corrispondano alle loro lunghezze di parola, ma anche in modo che non ci sia alcuna perdita di risoluzione. Una volta inseriti tutti i parametri nel Filter Designer e generato il filtro, il Filter Designer ci mostrerà la DFT (Trasformazione Discreta di Fourier) della risposta del filtro.

Ora possiamo esportarlo in un modello Simulink, dove possiamo eseguire un primo test e verificare se il modello quantizzato soddisfa i criteri definiti. Come input di simulazione, generiamo in MATLAB un segnale di somma dalle tre frequenze desiderate.

Figura 3

Inserire l’hardware nel sistema

Se il filtro si comporta in modo soddisfacente, con l’aiuto di HDL Coder possiamo generare il codice HDL (Hardware Description Language) per l’intero sistema, in modo da poter testare il filtro sulla scheda FPGA Eclypse Z7, ma non prima di aver apportato alcune modifiche al Modello Simulink in modo da poterlo fare.

La finestra HDL Block Properties ci permette di configurare i registri della pipeline e l’architettura in termini di moltiplicatori utilizzati. Dobbiamo scegliere uno dei tre diversi modelli di architettura: un’architettura completamente parallela, completamente seriale o parzialmente seriale.

Con l’architettura completamente parallela, la frequenza dei dati in uscita può essere uguale alla frequenza di clock e ogni moltiplicazione del filtro utilizzerà una sezione DSP dell’FPGA. L’implementazione completamente seriale, invece, utilizza una sola sezione DSP, ma la frequenza di uscita verrà ridotta a (velocità di clock) / (numero di moltiplicazioni), rallentando il calcolo. L’architettura parzialmente seriale, infine, si colloca nel mezzo, con il numero di slice selezionabili.

Questo ha lo svantaggio che aumenta il numero di elementi logici utilizzati. Dato che abbiamo abbastanza slice DSP sul SoC Zynq-7000 dell’Eclypse Z7, l’opzione completamente parallela è una buona scelta. Come ultimo passaggio qui, selezioniamo il linguaggio HDL di destinazione, il dispositivo utilizzato, il reset e i report desiderati nella pagina delle proprietà di HDL Coder. Dopo aver fatto tutte le configurazioni, possiamo generare il codice HDL per il nostro sottosistema.

Ora possiamo simulare il filtro con l’FPGA in-the-loop. Questo significa che l’algoritmo del filtro verrà eseguito direttamente sull’FPGA e non nel software sulla nostra workstation. È qui che entra in gioco lo strumento FIL (FPGA in-the-loop) di MATLAB. Questo ci permette, dopo aver creato la definizione della scheda, di connetterci ad essa.

Ora possiamo costruire il progetto e Vivado, lo strumento di sintesi e analisi HDL di Xilinx, si aprirà nella finestra comandi di MATLAB e sintetizzerà e implementerà il progetto demo FIL. Una volta che Vivado avrà terminato la sintesi, verrà aperto un modello Simulink che mostra il blocco FIL aggiunto. Ora possiamo collegare la scheda Eclypse Z7 e caricare il modello FIL nell’FPGA.

Figura 4: La schermata Block Parameter dello strumento FPGA in-the-loop

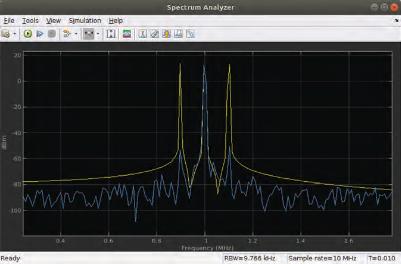

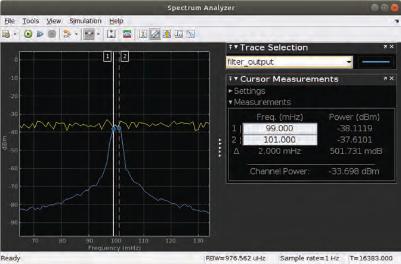

Per simulare la sorgente del segnale, è necessario aggiungere tre segnali sinusoidali che rappresentano le tre bande nella linea di trasmissione, con frequenze di 900 kHz, 1 MHz e 1,1 MHz. Per verificare l’output, abbiamo bisogno di una finestra dello Spectrum Analyzer. Al termine della simulazione, l’output contiene solo il segnale a 1 MHz.

Figura 5: La finestra Spectrum Analyzer mostra che solo il segnale sul canale 1 rimane dopo il filtraggio.

Acquisire i dati per la verifica

Dopo aver testato e verificato il filtro con l’FPGA in-the-loop possiamo creare l’applicazione finale, che utilizza non solo il filtro ma anche le schede ADC e DAC. Per questo, creiamo un progetto Vivado in cui aggiungeremo tutti i blocchi necessari, come lo Zynq-7000, i driver per i convertitori di dati e il generatore di clock.

Sul SoC Zynq-7000 non utilizzeremo il sistema di elaborazione, bensì solo la logica programmabile (PL). Come sorgente di clock, utilizzeremo il clock a 125 MHz dall’Ethernet PHY della scheda Eclypse Z7, che è collegata al PL.

È inoltre necessario un generatore di clock aggiuntivo per creare il clock di campionamento del filtro di 10 MHz e il clock di sistema di 100 MHz.

Come driver della scheda ADC, utilizzeremo l’interfaccia IP di AXI (Advanced eXtensible Interface)-Stream.

Quando aggiungiamo il filtro, dobbiamo gestire le dimensioni dei dati, perché l’output dell’IP AXI-Stream è grande 32 bit e contiene i dati di entrambi i canali dell’ADC. La parola corrispondente al canale 1 si trova sui 14 bit inferiori della parola, quindi deve essere estratta.

Lo stesso vale per il driver del DAC, in cui i bit di uscita superiori del filtro devono essere scartati, utilizzando un blocco Slice. Il nostro progetto di esempio utilizza entrambi i canali DAC: l’uscita del filtro è collegata al canale 1 e il segnale originale, come campionato dall’ADC, è collegato al canale 2 per consentirne la verifica tramite un oscilloscopio.

Una volta completata la progettazione del blocco, possiamo convalidarla, creare il wrapper HDL e generare il flusso di bit. Una volta sintetizzato e implementato il progetto, possiamo testarlo sulla scheda Eclypse Z7, insieme a un generatore di segnali e un oscilloscopio. Utilizzando un’onda sinusoidale da 1 MHz possiamo controllare la banda passante e, con un segnale da 910 kHz, la banda di arresto. Questa verifica indica che tutto funziona come previsto.

Un’altra possibilità è utilizzare un analizzatore logico, sia esso un dispositivo esterno o l’Integrated Logic Analyzer (ILA) di Xilinx, che può essere utilizzato per monitorare i dati di input e output all’interno dell’FPGA ed esportarli in MATLAB. Una terza possibilità è utilizzare la funzione FPGA Data Capture di MATLAB, che genera automaticamente un blocco IP che acquisisce dati in tempo reale dall’FPGA e li invia a MATLAB o Simulink tramite JTAG. FPGA Data Capture fa parte del pacchetto di supporto HDL Verifier per le schede FPGA Xilinx.

Nella finestra per la generazione del componente di acquisizione dati dell’FPGA, è possibile aggiungere le porte di ingresso e uscita del filtro e impostare la dimensione del buffer e la profondità massima della sequenza. Una volta terminato, lo strumento genererà il core IP dell’HDL, nonché uno script per avviare l’acquisizione dei dati dal workspace MATLAB e un modello Simulink per acquisire i dati da Simulink. L’ultimo passaggio consiste nell’aggiungere tutti i file al progetto e il modulo di acquisizione dati al design del blocco. Fatto questo, possiamo generare il flusso di bit.

Figura 6: Il blocco di progettazione che mostra l’IP AXI-Stream, la sezione di conversione della parola dati e il filtro passa-banda

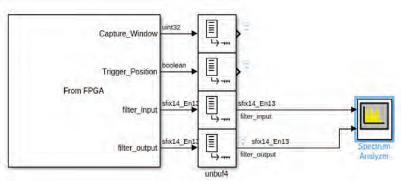

Per testare il sistema, dobbiamo spegnere il server hardware di Vivado in modo da liberare la porta JTAG. Sono necessarie anche alcune modifiche al modello di acquisizione dati Simulink, come la rimozione dell’oscilloscopio e la sua sostituzione con l’analizzatore di spettro e la configurazione del tipo e del formato dei dati.

Figura 7: Diagramma a blocchi per l’acquisizione dei dati in tempo reale sulla scheda Eclypse Z7

Con il rumore bianco proveniente da un generatore di segnale esterno, vediamo che il filtro funziona come previsto nell’intervallo di frequenza da 990kHz a 1010kHz senza attenuazione. Tuttavia, c’è un piccolo problema: la frequenza di aggiornamento dell’analizzatore è di 1Hz invece dei 10MHz del design reale.

Figura 8: Utilizzando un segnale di rumore bianco come input, il filtro lascia passare solo le frequenze da 990kHz a 1010kHz

Questo progetto dimostra che è possibile progettare facilmente un filtro digitale, controllarlo passo dopo passo e infine verificarlo con una scheda Eclypse Z7 Zinq-7000 come hardware in-the-loop, utilizzando i diversi pacchetti di MATLAB e Vivado.

Un tutorial completo passo-passo per questo progetto è disponibile qui

L’Eclypse Z7 è ora disponibile presso Farnell, il distributore autorizzato in Italia